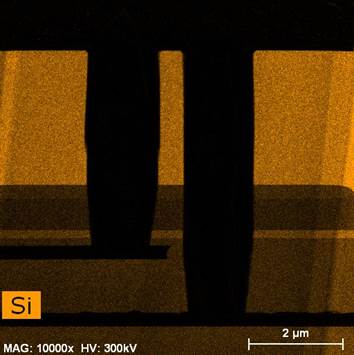

In recent decades, research and development in the field of micro- and nano- electronics has led to ever smaller structural sizes and continuously increasing integration densities of sensors, memories and processing circuits. Due to the physical limitation, the enormous technological growth regarding a wafer level is stagnating.

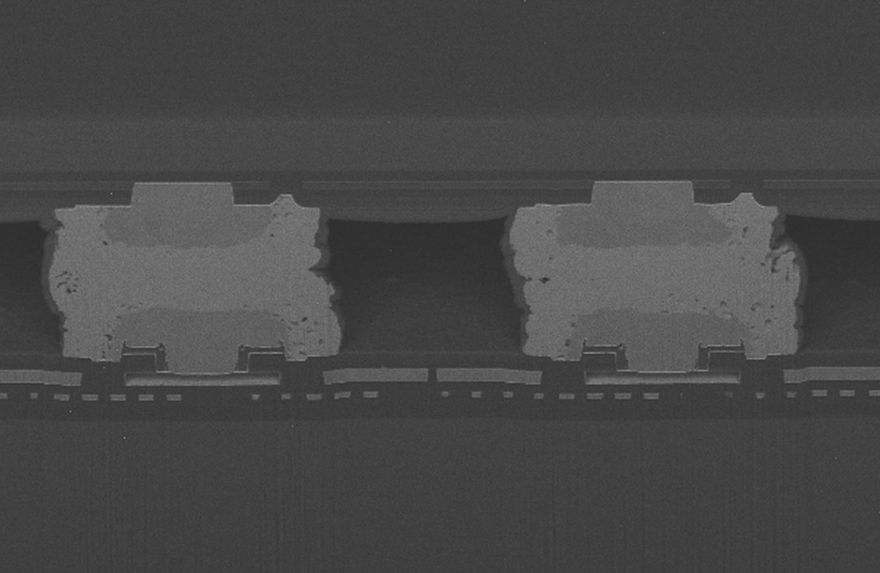

The 3D-Integration of micro- and nano-electric construction elements allows a vertical arrangement of different system devices and offers a way to continue the trend of compact and powerful devices (“More than Moore”)

3D-Integration offers further advantages:

- Cost reduction

- Shorter connecting paths

- Higher integration density

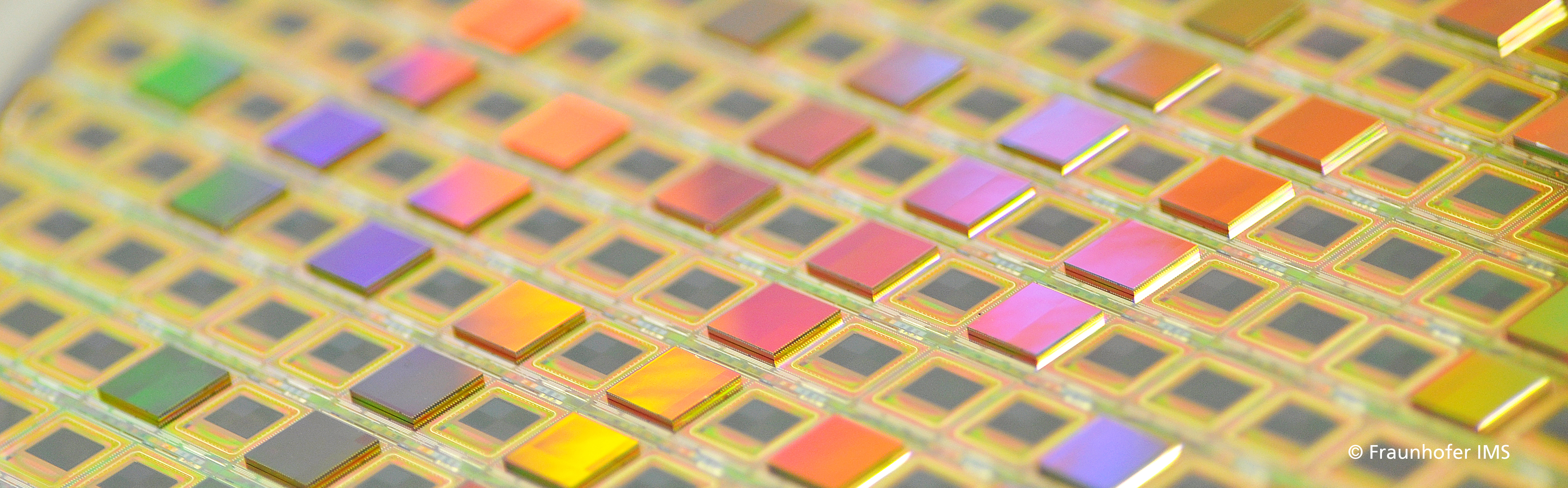

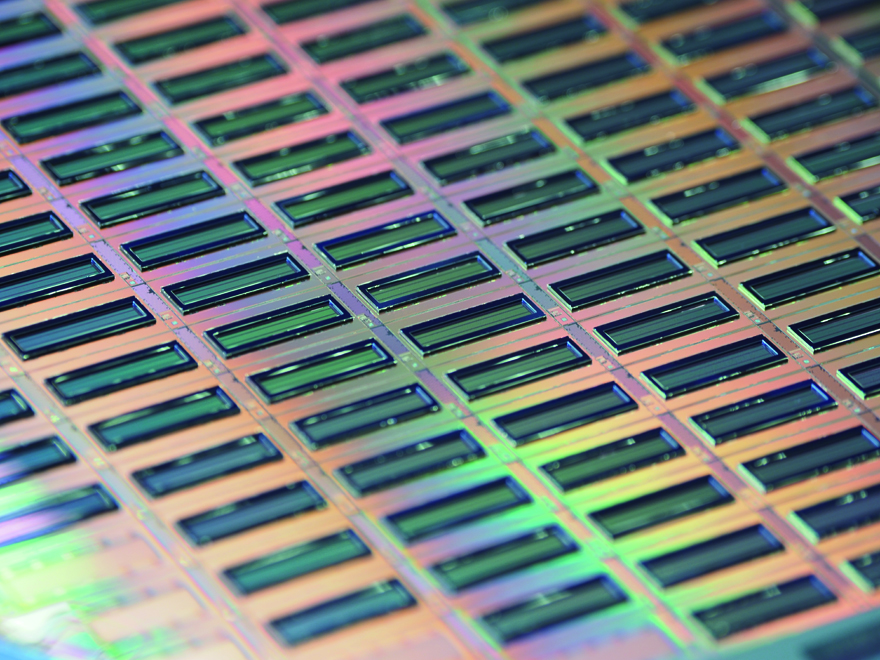

By exploiting the third dimension and the possibility of heterogeneous integration, structures from different process lines can be combined with a heterogeneous integration. Through 3D-Integration, e. g. optical sensors can be manufactured directly with the associated interpreting and signal processing circuit logic. Since current new developments place ever higher demands on the detectors, it is increasingly necessary to manufacture the detectors directly with the signal-processing circuit logic. Thus, for example, the interpreting circuit can be moved into the third dimension in order to increase the optically active area and thus the sensitivity.

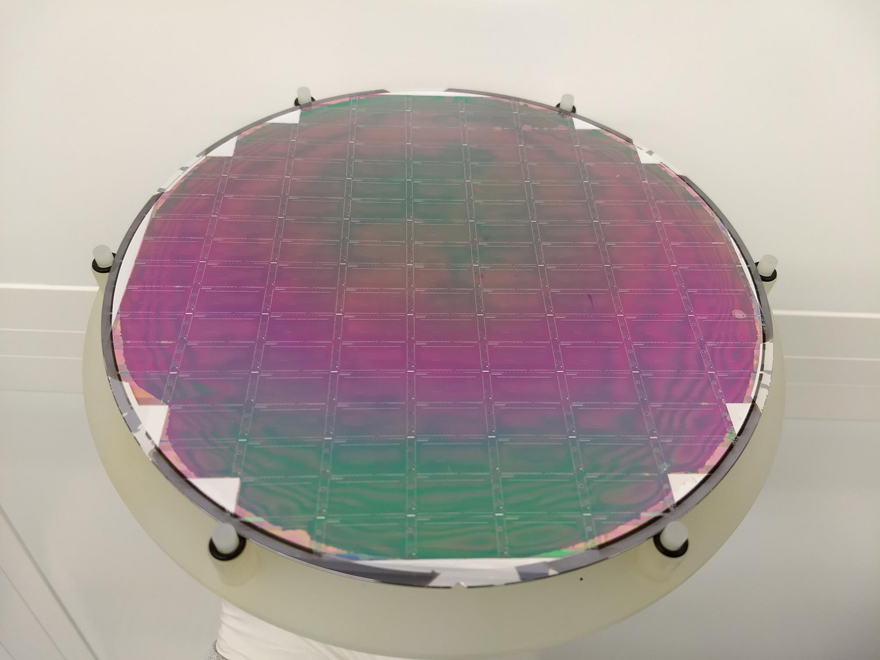

Fraunhofer IMS supports various technologies for 3D-Integration on 200 mm-wafers.