New AI hardware acceleration for smart sensor technology at Fraunhofer IMS

RISC-V processor AIRISC accelerates sensor data analysis by 80 %

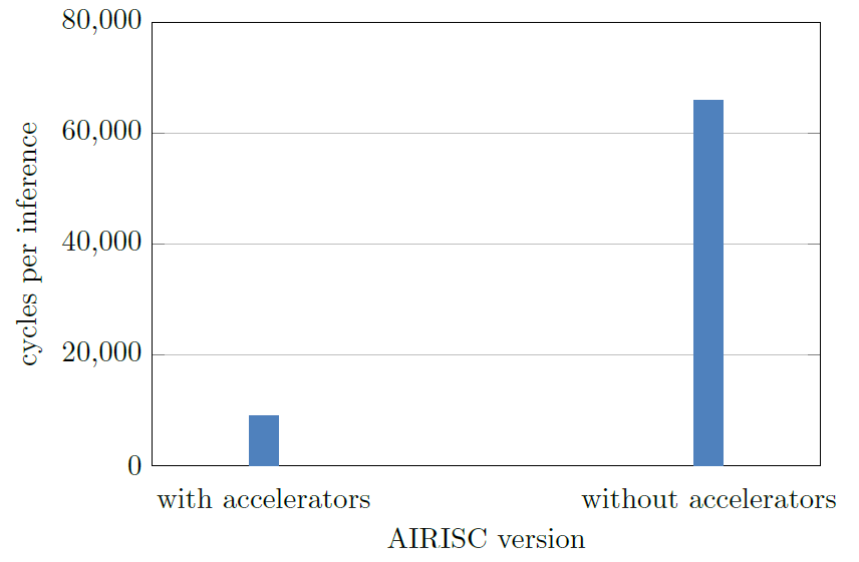

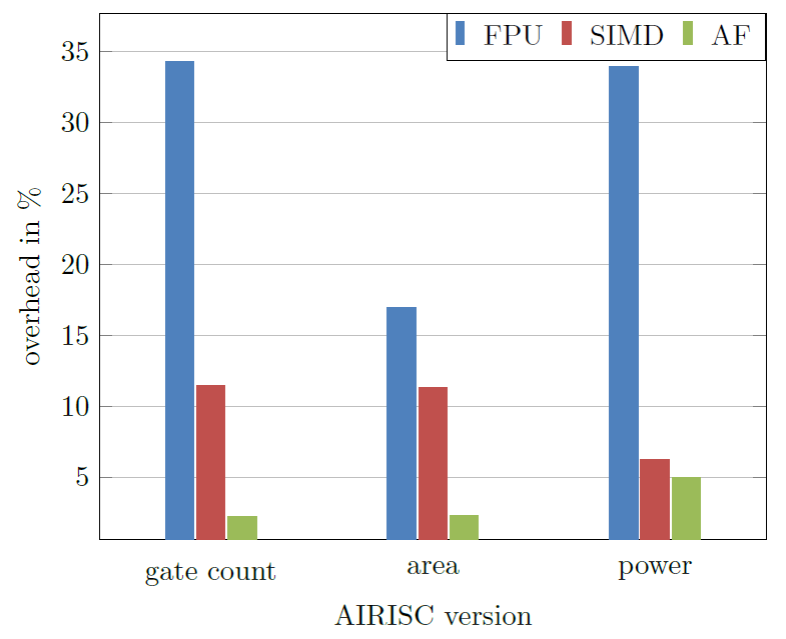

The RISC-V processor AIRISC, a 32-bit RISC (Reduced Instruction Set Computer) architecture, now features instruction set extensions and coprocessors for efficient neural network computation. For a medical application to detect atrial fibrillation in ECG data, we achieved a speed advantage of over 80% in evaluation with only 10% higher area and power requirements.

AIRISC and current research on application-specific enhancements.

As of early 2022, the RISC-V processor AIRISC for embedded and sensing applications is available as a free download on GitHub in its base variant. This version is under the permissive Solderpad license and comes with sample projects for various FPGA development boards. The license not only allows testing of the core, but also its use in custom and commercial applications. To support this, the Fraunhofer Institute for Microelectronic Circuits and Systems is researching modular, application-specific extensions, for example for real-time control in power electronics, for signal analysis in medical applications and for 3D image processing using LIDAR.

The new accelerator package

The latest result of these developments is a package of accelerators for efficient neural network execution. With the accelerators, modern AI algorithms also work on energy-critical hardware, such as energy-autonomous sensor systems. To create benchmarks, we have ported our optimized software framework "AI for Embedded Systems - AIfES" to the AIRISC core in addition to Tensor Flow Lite.

The current AIRISC extension package consists of two components:

1. a collection of hardware accelerators for common activation functions (AF). As of March 2022, these include tanh, sigmoid, softsign, and softmax based on the e-function.

2. parallel execution of multiple multiply and add operations (multiply-accumulate) to accelerate matrix multiplications. Currently the data types 16-bit integer (two parallel units) and 8-bit integer (four parallel units) are supported. The extension replaces the standard ALU (Arithmetical Logical Unit) and uses the minimum possible hardware overhead at maximum speed by direct integration into the processor pipeline. These additionally introduced SIMD (Single Instruction Multiple Data) instructions are compatible with the P-Extension of the RISC-V specification for DSP applications, which is currently in the ratification phase (expected by Q4'22).

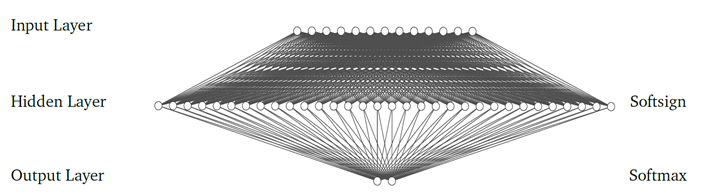

A feed-forward neural network with 13 neurons in the input layer, a hidden layer with 17 neurons, and two neurons in the output layer serves as a benchmark for the accelerators described. This network originates from an application to examine ECG data for signs of atrial fibrillation.

By using the hardware accelerators, a speed advantage of more than 80 % can be achieved in the execution of the neural network (Fig. 1). In addition to the parallel execution of the matrix multiplications, a large proportion of memory accesses is also saved here, which is why the improvement is well above the expected factor of four.

The data type used is 8-bit integer. The activation functions used are softsign for the hidden layer and softmax for the output layer (Fig. 2).

Figure 3 shows the overhead in hardware gates (gate count), area and power dissipation involved in the described accelerators. The values refer to the synthesis of the processor for a 0.18 µm CMOS technology as an example. In addition, the space required by the hardware floating point unit (FPU), which is also available for AIRISC, is shown.

The next steps with AIRISC at Fraunhofer IMS

The enormously speed advantage is offset by a very moderate overhead in hardware requirements. By significantly reducing the operating frequency, a considerable portion of the required power consumption of the system can thus be saved. Details were presented at the fifth meeting of the Duisburg RISC-V group. The presentation is available on the RISC-V International Youtube channel.

With the "AIRISC-PWR", Fraunhofer IMS already offers an integrated RISC-V PWM and controller solution for use in power electronics. A radiation resistant version of the AIRISC for use in large-scale physical experiments is also available. In addition, we are already developing the next member of the AIRISC family: "AIRISC-LIDAR" is a set of extensions specialized for processing raw LIDAR data for use in FPGA and ASIC.

Fraunhofer IMS is also gradually extending the Safety variant of AIRISC "AIRISC-SFTY" for applications with functional safety requirements. This safety AIRISC features mechanisms such as dual-core lockstep, ECC memory safeguards (Error Correcting Code) and hardware watchdog and is certified according to ISO 26262 ASIL-D Ready. It will be available in mid-2022.

For more information and datasheets, please visit www.airisc.de

Please direct inquiries to Mr. Carsten Rolfes, Program Manager Trusted Electronics as well as Mr. Alexander Stanitzki, Business Unit Manager Industry.