News about the RISC-V processor AIRISC

AIRISC - the RISC-V Processor for Smart Sensors and Embedded AI Applications of Fraunhofer IMS

News about the AIRISC family of RISC-V cores from Fraunhofer IMS.

The AIRISC enables efficient machine learning and AI in sensors, IoT devices and other embedded applications. The free RISC-V processor instruction set is ideally suited to implement custom extensions in a short time to provide optimal performance for specific applications. In combination with the AIfES software library developed by Fraunhofer IMS, the AIRISC processor family supports neural network inference and training directly on the embedded device.

For this purpose, we have compiled recent results and developments. More technical details about AIRISC can be found in the product info sheet, which is available for download under www.airisc.de.

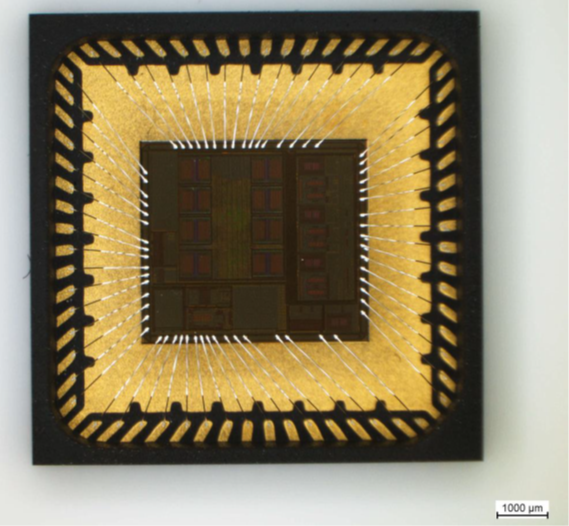

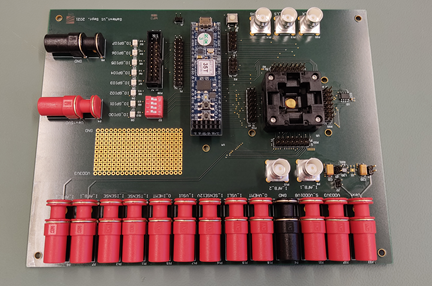

Successful AIRISC Tapeout

In two projects, executable chips with the AIRISC as the central processor for control and data processing have been developed in the meantime. The 180 nm technology of XFAB was used and the chips were provided with a package by the colleagues of Fraunhofer ENAS, so that they are currently being tested extensively at the IMS.

In the DFAM project SichEL, the AIRISC was coupled with a capacitive Physical Unclonable Function to generate a unique identification number for traceability of the chip within the supply chain. In addition, the PUF enables the derivation of cryptographic keys.

In the GaNext project, the AIRISC was enhanced with safety mechanisms, acceleration for AI algorithms, multi-channel ADC and high-precision PWM generation to control GaN power modules.

Upcoming updates in 2022

Release of an Open Source Version

In order to make it easier for interested parties to get started with AIRISC and also to give them the opportunity to make their own adjustments, we are currently preparing the release of a basic version under an open source license.

In addition to the actual processor core and the extensions M, C and F, the freely available version will also include common peripherals such as an MTIME-compatible timer or interfaces such as GPIO, UART and SPI. The freely available AIRISC thus already enables use under real conditions.

Product AIRISC is certified ASIL-D ready

Fraunhofer IMS is also working on an ASIL-D ready certified dual-core lockstep variant of AIRISC for safety-critical applications, e.g. in the automotive sector.

Both variants will be available during 2022.

AI enhancements

Also in the first half of 2022, there will be a special version of AIRSC for Tiny-ML applications. With hardware support for the RISC-V ISA P extension and the integration of various HW activation functions, the AIRISC together with the AI framework AIfES will enable new application possibilities. In addition to the execution of AI models, this also enables training directly in microcontrollers.

RISC-V Duisburg Meetup

Our colleague Alexander Stanitzki is also on the road as a RISC-V Ambassador and hosts the, unfortunately currently only digital, Meetups of the RISC-V Group Duisburg.

In 2021 there were already 3 events where current developments around the AIRISC and by guest speakers from the RISC-V ecosystem were presented. The videos of the past events are available online and the next meeting is scheduled for February 16, 2022.

AIRISC in the radiation-hard chip - Tapeout of the University of Applied Sciences Dortmund

In addition to own chips, the AIRISC is also successfully used by partners. The team of the laboratory for "Integrated Circuit Design" at the FH Dortmund University of Applied Sciences and Arts, around Prof. Michael Karagounis and the PhD student Alexander Walsemann has built a radiation-hard, triple-redundant chip in a 65 nm technology from TSMC with the AIRISC.

LinkedIn product pages AIRISC and AIfES

We are now also on Linkedin. If you are interested in current information about the products AIRISC, the RISC-V processor of the Fraunhofer IMS or the embedded AI framework AIfES, please have a look.

AIfES – KI Framework

AIRISC –RISC-V Prozessor für Safety, Security und KI