Forschung und Entwicklung im Bereich der Mikro- und Nano-Elektronik führten in den letzten Jahrzehnten zu immer kleineren Strukturgrößen und kontinuierlich wachsenden Integrationsdichten von Sensoren, Speichern und verarbeitenden Schaltungen. Durch die physikalische Limitierung stagniert jedoch das enorme technologische Wachstum hinsichtlich einer Waferebene. Die 3D-Integration von mikro-/nanoelektrischen Bauelementen ermöglicht eine vertikale Anordnung von verschiedenen Systemkomponenten und bietet einen Weg den Trend von kompakten und leistungsstarken Bauelementen fortzusetzen (»More than Moore«). Durch 3D-Integration erschließen sich einhergehend mit der dicht gepackten Bauform weitere Vorteile:

- Kostenreduktion

- kürzere Verbindungswege

- höhere Integrationsdichte

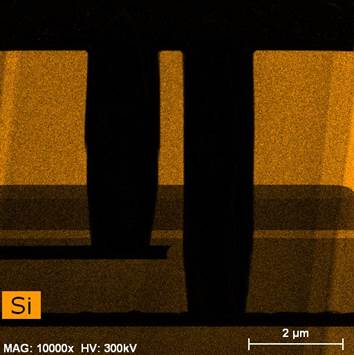

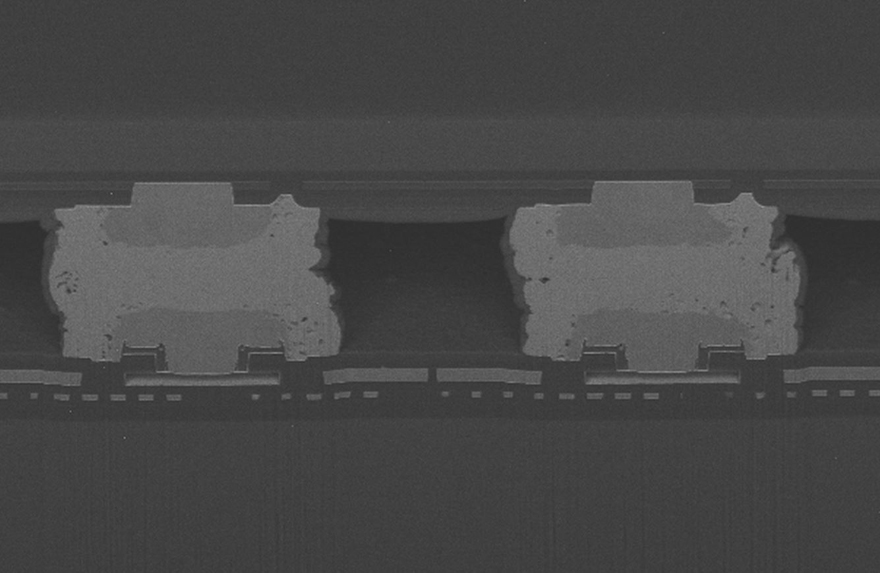

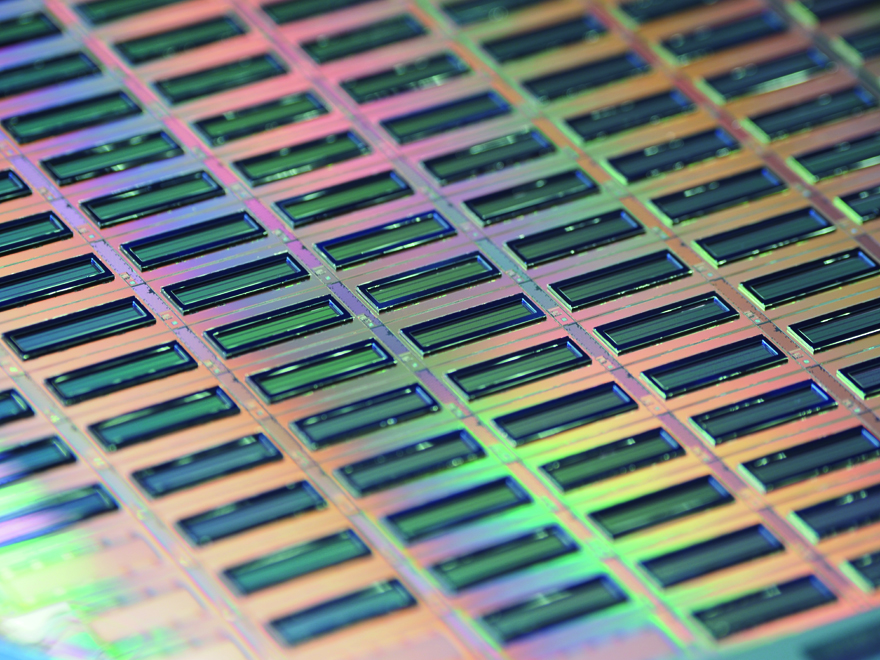

Durch Ausnutzung der dritten Dimension und der Möglichkeit einer heterogenen Integration, können Strukturen aus unterschiedlichen Prozesslinien miteinander vereint werden. Durch die 3D-Integration können z. B. optische Sensoren direkt mit der zugehörigen interpretierenden und signalverarbeitenden Schaltungslogik gefertigt werden. Da aktuelle Neuentwicklungen immer höhere Ansprüche an die Detektoren stellen, ist es vermehrt notwendig, die Detektoren direkt mit der signalverarbeitenden Schaltungslogik zu fertigen. Somit kann z. B. die interpretierende Schaltung in die dritte Dimension ausgelagert werden, um die optisch aktive Fläche und damit die Sensitivität zu erhöhen

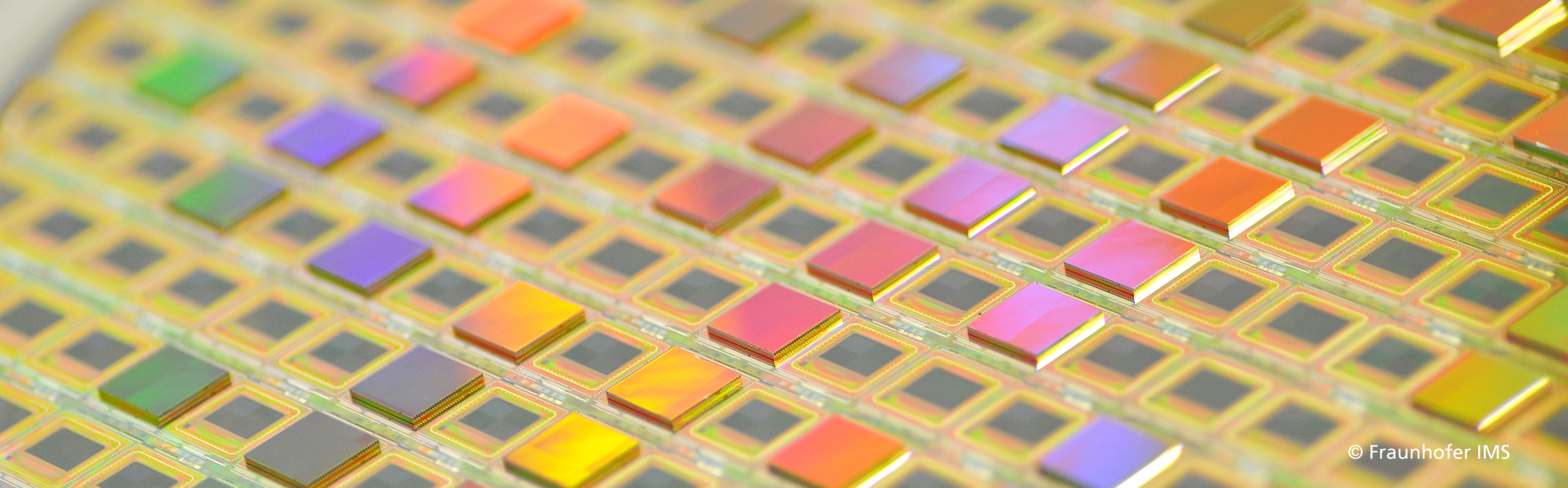

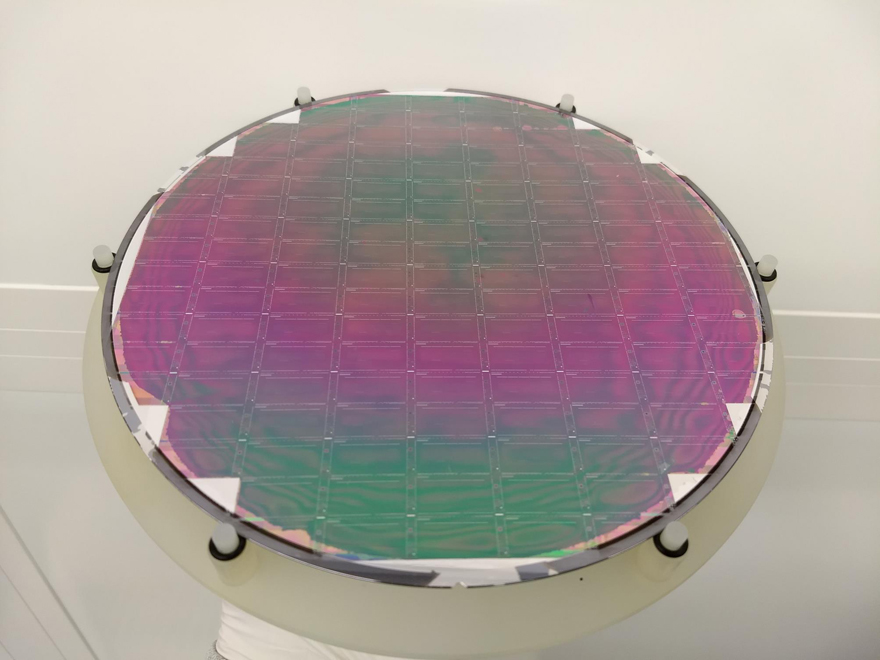

Fraunhofer IMS unterstützt dabei verschiedene Technologien zur 3D-Integration auf 200 mm-Wafern.