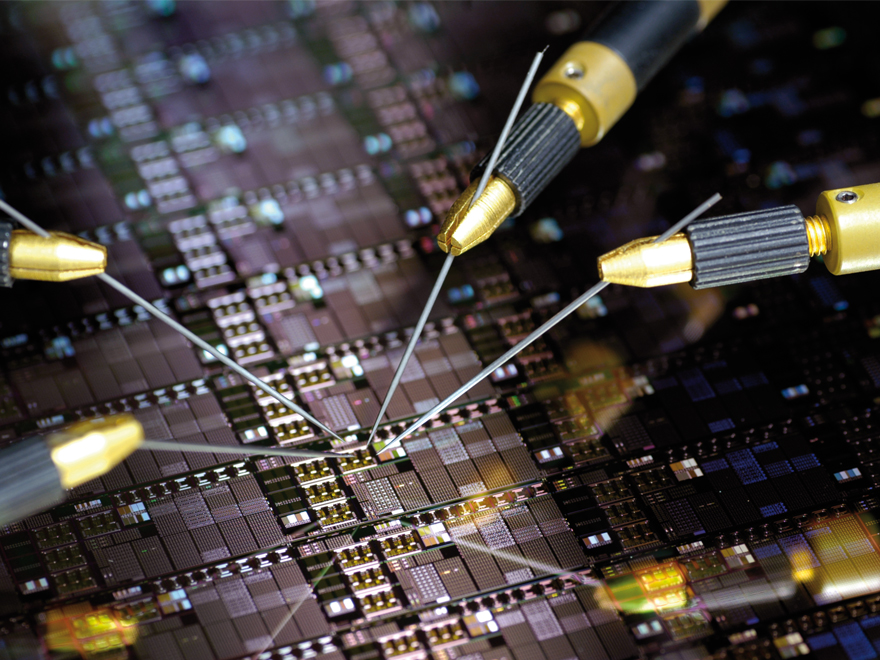

Die Themen funktionale Sicherheit und Cybersicherheit spielen bei der Spezifikation und dem Entwurf moderner integrierter Schaltungen eine immer größere Rolle. Diese Schaltungen beinhalten neben einem spezialisierten Analogteil und kundenspezifischer Schnittstellen häufig auch eingebettete Prozessorkerne.

Insbesondere bei der Auswahl der zu integrierenden Prozessoren stellt sich die Frage nach einer geeigneten Architektur, welche Anforderungen an die Funktionale Sicherheit gewährleistet und robust gegenüber Cyberattacken ist.

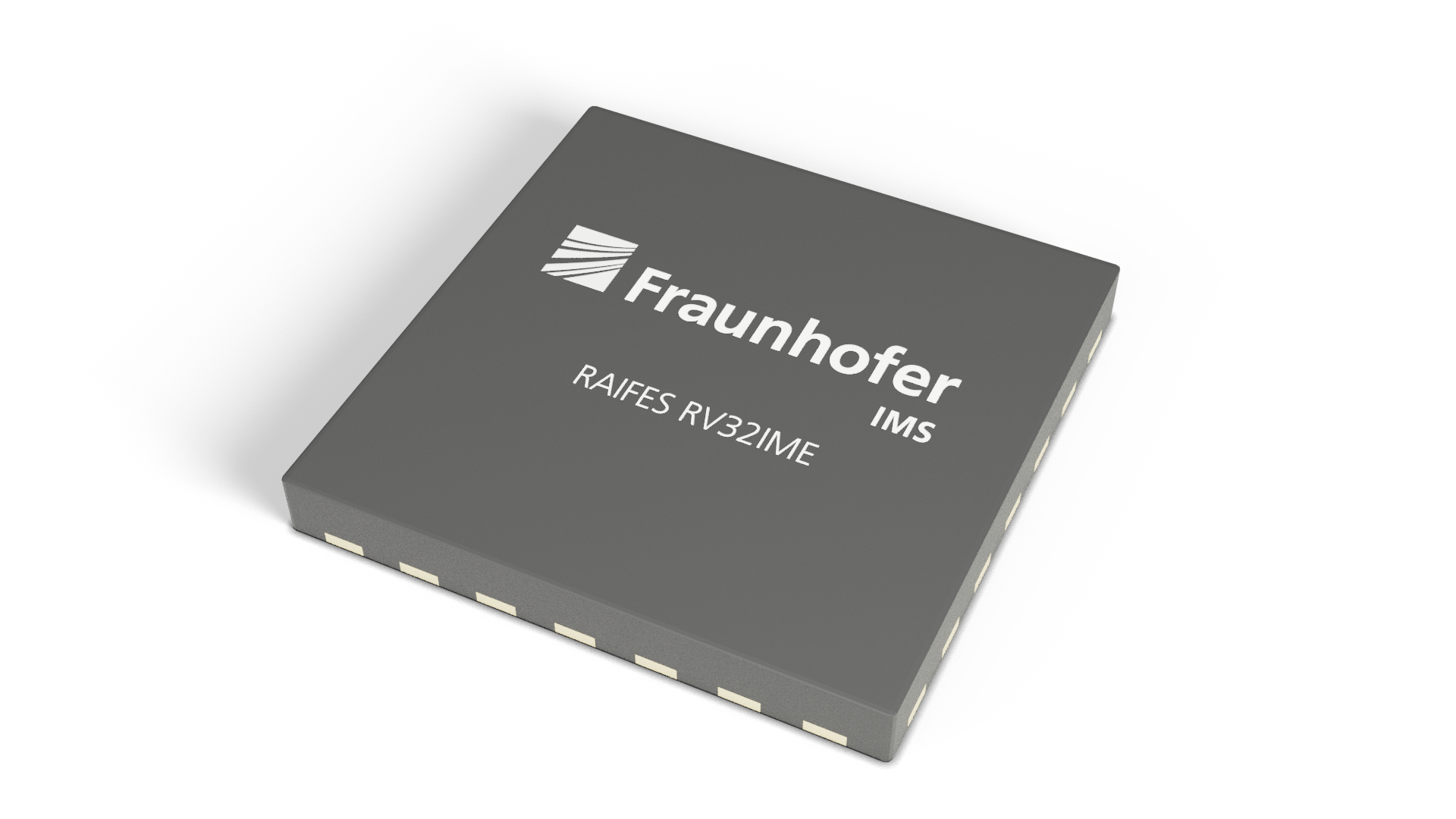

Das Fraunhofer IMS bietet abgesicherte Prozessorkerne auf Basis der offenen RISC-V Architektur an. Diese Befehlssatz-Architektur erlaubt die Entwicklung von kundenspezifischen Spezialprozessoren für Safety & Security und ermöglicht eine hochgradige Optimierung der Kerne auf eine Anwendung. Im Gegensatz zu vollständig proprietären Lösungen werden diese Spezialprozessoren durch den einheitlichen Befehlssatz jedoch weiterhin von einer großen Anzahl von Entwicklungsumgebungen und Softwarepaketen unterstützt (z. B. Eclipse IDE oder GNU toolchain). Zudem entfallen die mitunter hohen Lizenzkosten für die Verwendung anderer verbreiteter Controller-Kerne.

RISC-V insbesondere auch für preissensible Applikationen

Als Basis-Kerne stehen flächenoptimierte Implementierungen für preissensible Applikationen in der Industrie zur Verfügung.

In diesen Applikationen ist die Aufgabe des Prozessorkerns üblicherweise auf einen bestimmten Bereich wie z. B. Regelschleifen, die Linearisierung von Sensordaten der die Implementierung verschiedener Protokoll-Stacks beschränkt. Diese Aufgaben können mit einem Basis-Kern und wenigen spezialisierten Teilen (Coprozessoren oder Peripheriemodulen) oft kostengünstig gelöst werden.

In diese Basis-Kerne können Zusatzmodule für die Cybersicherheit, wie z. B. sichere Schlüsselspeicher, Kryptobeschleuniger, oder Manipulations- und Firmwareschutz integriert werden. Das Fraunhofer IMS stellt hier angepasste Lösungen für vertrauenswürdige Hardwareplattformen zur Verfügung.

Integrierte Safety- und Security-Funktionalität

Durch die Integration von Überwachungsfunktionen und die redundante Auslegung kritischer Teile der Schaltung kann der Einsatz in ausfallsicheren, SIL-zertifizierten Systemen bis SIL 3 bzw. ASIL D unterstützt werden.

Sichere Schlüsselspeicher dienen dabei dem Schutz kryptographischen Materials vor Manipulation oder unbefugtem Auslesen. Hierzu können speziell abgesicherte nichtflüchtige Speicher verwendet werden. Alternativ kann das Schlüsselmaterial direkt aus den Materialeigenschaften des gefertigten Chips extrahiert werden, was als »Physical Unclonable Function« (PUF) bezeichnet wird.