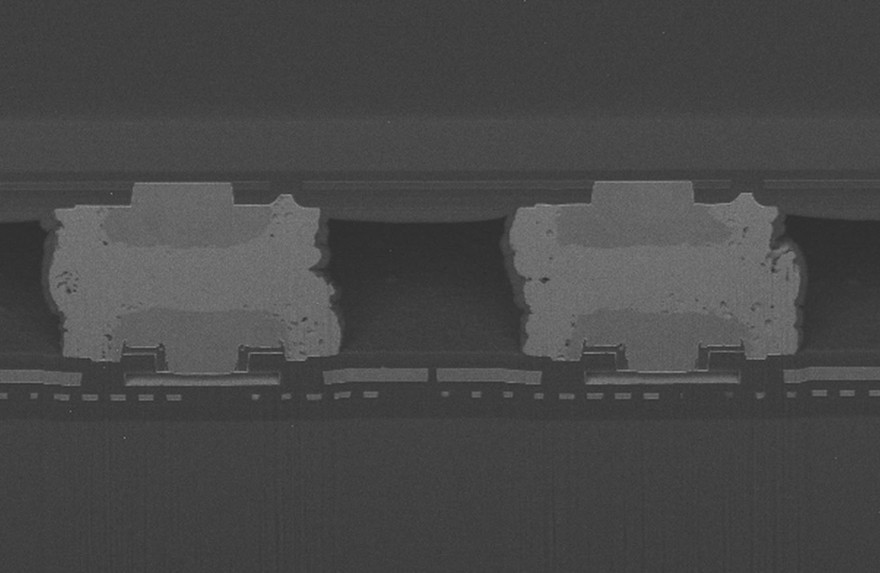

Durch Ausnutzung der dritten Dimension und der Möglichkeit einer heterogenen Integration, können Strukturen aus unterschiedlichen Prozesslinien miteinander vereint werden. Durch die 3D-Integration können z. B. optische Sensoren direkt mit der zugehörigen interpretierenden und signalverarbeitenden Schaltungslogik gebondet werden. Da aktuelle Neuentwicklungen immer höhere Ansprüche an die Detektoren stellen, ist es vermehrt notwendig, die Detektoren in spezialisierten Technologien herzustellen und die signalverarbeitenden Schaltungsteile in einer Technologie mit sehr kleinen Strukturen zu fertigen. Dadurch wird z. B. die interpretierende Ausleseschaltung in die dritte Dimension ausgelagert und die optisch aktive Fläche vergrößert und damit die Sensitivität erheblich erhöht.

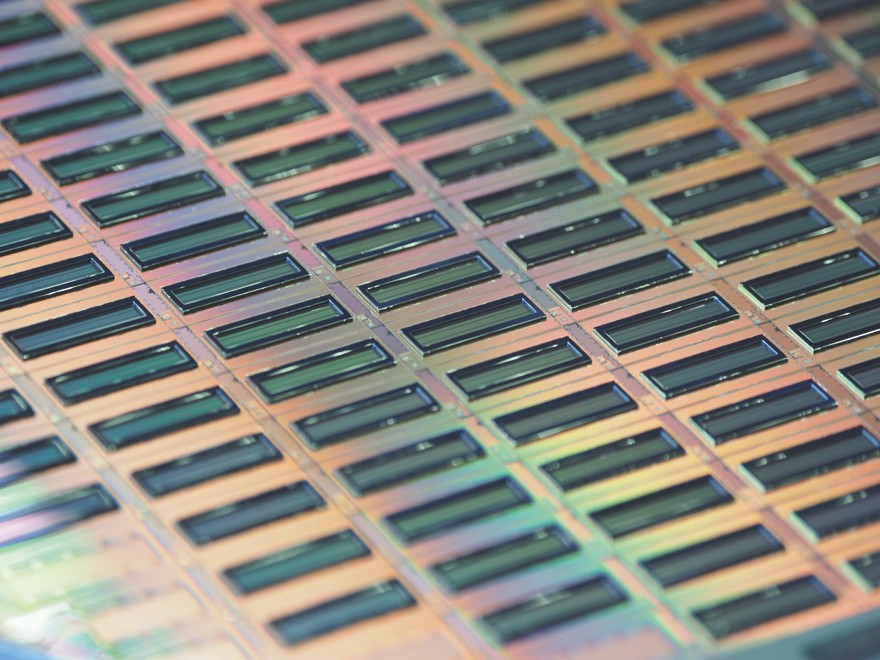

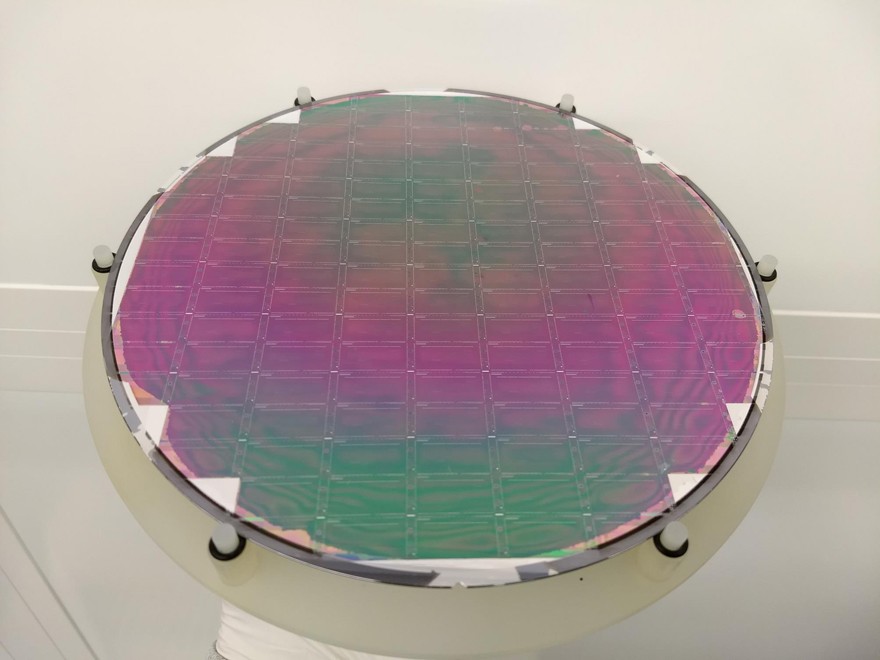

Fraunhofer IMS unterstützt dabei verschiedene Technologien zur 3D-Integration auf 200 mm-Wafern.

Wafer-zu-Wafer-Bonding

Das Fraunhofer IMS verfügt über ein direktes Oxid-zu-Oxid-Bondverfahren zur 3D-Integration, welches bei CMOS-kompatiblen Temperaturen unter 400 °C erfolgt. Das direkte Waferbonden basiert auf der Ausbildung von kovalenten Siloxan(Si-O-Si)-Verbindungen. Hierzu werden die Waferoberflächen im Sauerstoffplasma aktiviert, um unter einer H2O-Atmosphäre Silanol (Si-OH)-Gruppen zu erzeugen. Die Wafer werden zueinander ausgerichtet und kontaktiert, so dass sich im Bereich des Bondinterfaces Wasserstoffbrückenbindungen bilden. Abschließend wird das Waferpaar auf über 250 °C erhitzt und durch die Abdiffusion von Wasser bilden sich starke kovalente Siloxan-Verbindungen. Zur Herstellung eines qualitativ hochwertigen Bonds müssen folgende Oberflächeneigenschaften beachtet werden:

Topologie, Mikrorauigkeit, Biegung, Partikelkontamination

Durch langjährige Erfahrungen am Fraunhofer IMS in CMOS- und MEMS-Prozessen sowie in der Aufbau- und Verbindungstechnik, konnten optimierte Stresskompensations- und chemisch mechanische Planarisierungsverfahren (CMP) sowie angepasste Layout-Designs für das W2W Bonden entwickelt werden. Mit den Prozessoptimierungen wird eine Scherfestigkeit von über 4 kg/mm2 und eine Präzisionsgenauigkeit des Waferbonds von unter 2 µm erreicht.

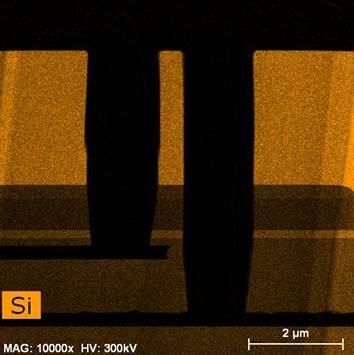

Die Vorderseiten-Silizium-Durchkontaktierung (TSV: Through Silicon Vias) geschieht über µVias, welche mit einem ALD (Atomic Layer Deposition, Atomlagenabscheidung)-optimierten Materialstapel gefüllt werden. Durch verschiedene µVia-Varianten kann der Prozess an individuelle Kundendesign-Vorgaben angepasst werden.