Das Fraunhofer IMS hat ein Chip-Scale-Package (CSP) für kundenspezifische Mikrosysteme, wie zum Beispiel MEMS Resonatoren oder Beschleunigungssensoren entwickelt. Es bietet erhebliche Vorteile gegenüber klassischen Gehäusen aus Metall, Kunststoff oder Keramik, da es kaum größer als der Chip selbst ist. Weiterhin wird eine Verkapselung der Sensoren im Vakuum oder Intergasen bei niedrigen Kosten sowie einer Skalierbarkeit zur großen Stückzahlen ermöglicht.

Das Fraunhofer IMS hat durch die Entwicklung eines Vakuum Chip-Scale-Packages mit integriertem Infrarot-transparentem Fenster das kleinstmögliche Vakuumgehäuse für ungekühlte IR-Imager realisiert. Mikrobolometer als Sensorelemente eines ungekühlten Infrarotsensors funktionieren nach dem thermischen Prinzip und müssen daher zur Reduzierung von thermischen Verlusten infolge von Gaskonvektion in einem Vakuumgehäuse betrieben werden. Dieses Vakuum Chip-Scale-Package enthält ein IR-transparentes Fenster mit einer Antireflektionsschicht und weist neben dem Größenvorteil auch erhebliche Kostenvorteile durch den integrierten Herstellungsprozess auf. Die Technologie des Vakuum Chip-Scale-Packages kann auch universell für Vakuum- oder Schutzgehäuse in Anwendungen außerhalb von ungekühlten Infrarotsensoren eingesetzt werden.

Das Vakuum Chip-Scale-Package besteht im unteren Teil aus dem CMOS-Substrat, das die Ausleseschaltung (ROIC) und das Mikrobolometer-Array beinhaltet. Ein elektrochemisch abgeschiedener Lötrahmen umgibt dabei das Mikrobolometer-Array. Mittels eines Flip-Chip-Prozesses wird jeweils ein IR-transparenter Deckel mit einer breitbandigen, beidseitigen Antireflektionsschicht auf dem Lötrahmen platziert. Im Waferverbund erfolgt schließlich ein Vakuum-Lötprozess, bei dem der Lötrahmen mit dem IR-transparenten Deckel hermetisch versiegelt wird und somit eine Mikro-Kavität mit einem sehr guten Vakuumlevel um das Mikrobolometer-Array herum realisiert wird. Um das Vakuumniveau und die Langzeitstabilität zu gewährleisten, wird während des Lötprozesses ein Getter, der sich auf der Innenseite des Deckels befindet, aktiviert.

Bei dem vom Fraunhofer IMS entwickelten Vakuum Chip-Scale-Package werden die IR-transparenten Deckel nur auf als »gut« getesteten Ausleseschaltungen platziert. Weiterhin lässt sich die Größe der IR-transparenten Deckel unabhängig von der Größe der Ausleseschaltung optimieren, so dass sich auf einem Deckel-Wafer deutlich mehr IR-transparente Deckel befinden, als auf einem Substratwafer Ausleseschaltungen enthalten sind. Auch das Sägeverfahren zum Vereinzeln der Ausleseschaltungen des Substratwafers ist deutlich vereinfacht, da nicht aufwändig über mehrere Sägeschritte der Padkranz zum elektrischen Anschluss der Ausleseschaltungen freigelegt werden muss. Durch diese Form des optimierten Waferlevel-Prozesses ergeben sich deutliche Kostenvorteile beim realisierten Vakuum-Gehäuse im direkten Vergleich zum klassischen Waferlevel-Package, bei dem für jeden Substratwafer ein eigener kompletter Deckelwafer benutzt werden muss.

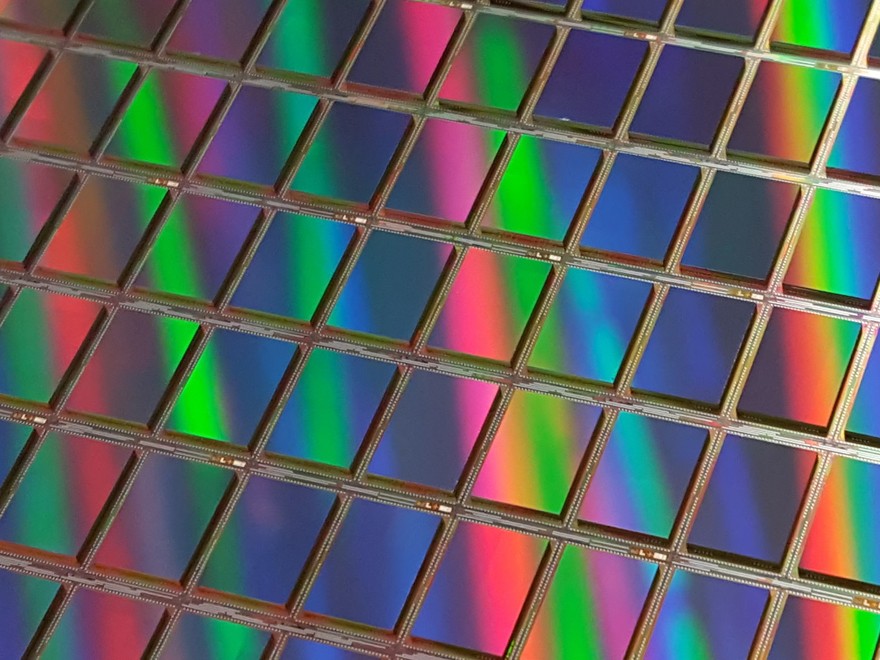

Die gesamte Herstellung der Chip-Scale-Packages erfolgt im Mikrosystemtechnik Lab&Fab des Fraunhofer IMS auf 200 mm Wafern. Hierfür können sowohl am Fraunhofer IMS hergestellte, als auch von Kunden bereitgestellte Wafer verwendet werden. Auch die für die Verkapselung verwendeten Deckel können am Fraunhofer IMS an die Zielanwendung angepasst und hergestellt werden. Durch die geeignete Wahl der Deckelgröße können die Bondpads der Mikrosystem-Chips nach der Herstellung des Chip-Scale-Packages frei zugänglich sein, so dass noch auf Wafer-Ebene ein Funktionstest möglich ist und hiernach Chips für die Weiterverarbeitung nach dem Vereinzeln ausgewählt werden können.