AIRISC Family - RISC-V Prozessoren für Industriesteuerung, medizinische Sensorik, Sicherheit und viele mehr

Profitieren Sie von unseren SoC-Design Services

- Von Konzept- und Machbarkeitsstudien bis zur Erstellung kompletter Entwürfe und Support

- Mixed signal Systemdesign basierend auf RISC-V Prozessoren für intelligente Sensoren

- Entwicklung von FPGA-basierten und kundenspezifischen ASIC-Lösungen

- Funktionale und Cybersicherheit für kritische Anwendungen in der Luft- um Raumfahrt, im Automobil- und Industriesektor

- Effiziente Hardware für Inferenz und Training von neuronalen Netzen

Vertrauenswürdige RISC-V Cores

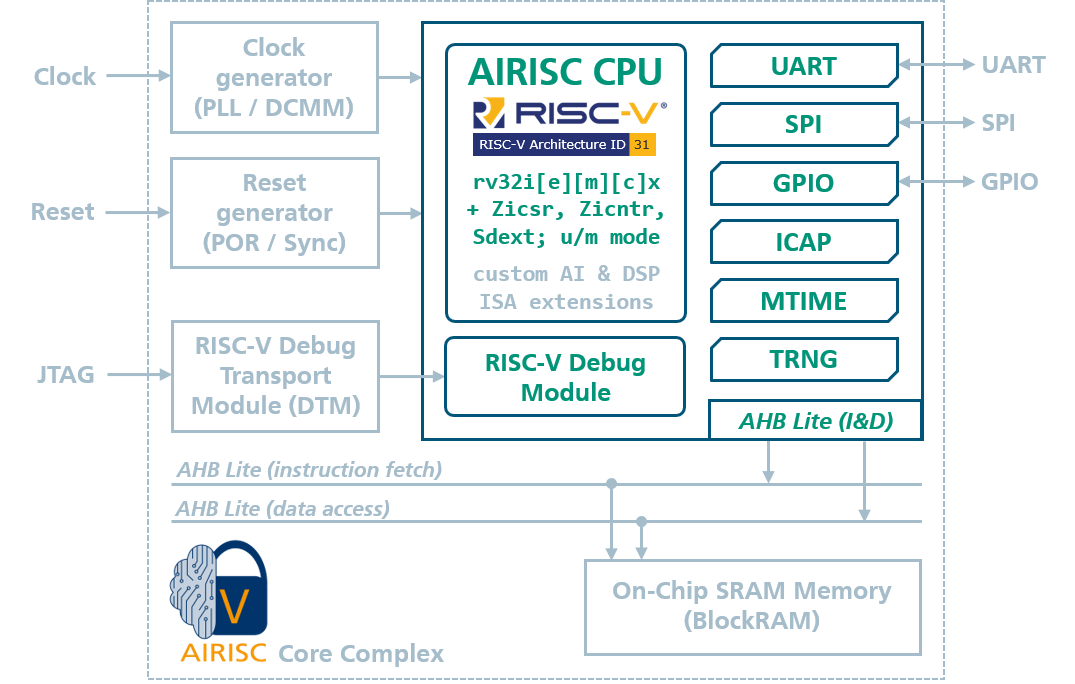

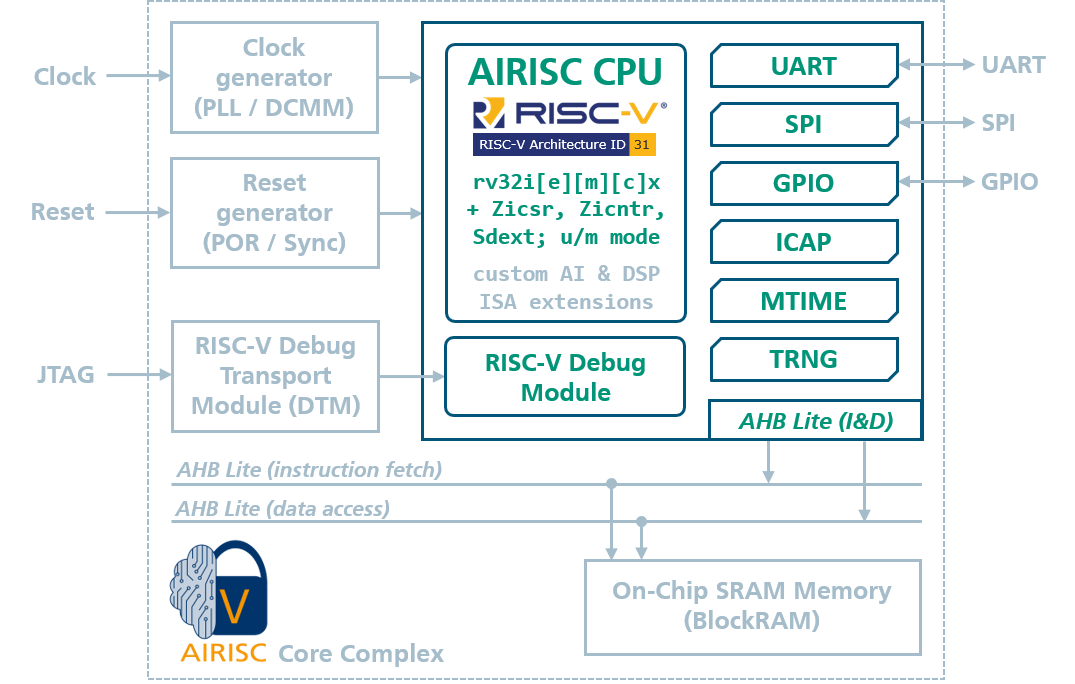

Die vom Fraunhofer IMS entwickelte AIRISC-Familie ermöglicht effizientes maschinelles Lernen und KI in Sensoren, IoT-Geräten und anderen eingebetteten Anwendungen mithilfe von RISC-V Prozessoren. AIRISC-Varianten mit erweiterten Sicherheitsmechanismen wie Dual-Core-Lock-Stepping (DCLS) oder Error Correcting Codes (ECC) sind für den Einsatz in ausfallsicheren Systemen nach ISO 26262 (bis ASIL-D) und DIN 61508 verfügbar. Da der Schutz des geistigen Eigentums in diesen Anwendungen sehr wichtig ist, bietet die AIRISC-Familie kryptographische Sicherheitsfunktionen wie Firmware-Schutz und sicheres Booten. Die freie RISC-V-Architektur ermöglicht es, kundenspezifische Erweiterungen in kurzer Zeit zu implementieren und so eine optimale Rechenleistung für spezielle Anwendungen bereitzustellen. Diese Eigenschaften machen AIRISC zur besten Wahl für eingebettete Echtzeit-Sensoranwendungen und die Integration in IoT-Systeme.

Für Embedded AI entwickelt

Im Zusammenspiel mit der vom Fraunhofer IMS entwickelten AIfES®-Softwarebibliothek (AI for Embedded Systems) unterstützt die AIRISC-Prozessorfamilie die Inferenz und das Training von neuronalen Netzen direkt auf dem eingebetteten Endgerät. Integrierte Beschleuniger ermöglichen verteiltes Training in vernetzten Geräten (federated learning) und auch die Kalibrierung von Sensoren mittels KI. Die Datenverarbeitung direkt im Sensor, ohne die Notwendigkeit einer permanenten Kommunikation mit der Cloud, macht den AIRISC-Prozessor für energieautarke und tragbare Sensorsysteme interessant. Er ermöglicht den Entwurf kompakter, die Privatsphäre schützender, Systeme und ISA-Erweiterungen (engl. Industry Standard Architecture).

AIRISC Projekte

Halbleiter-Chip mit integrierter künstlicher Intelligenz detektiert Herzerkrankungen

Vorhofflimmern gehört mit fast zwei Millionen Betroffenen zu den großen Volkskrankheiten in Deutschland. Ein zu spät erkanntes VHF kann für Patienten fatale Folgen wie einen Schlaganfall nach sich ziehen. Durch eine frühzeitige Intervention könnten solch schwere Auswirkungen vermieden werden. Unter maßgeblicher Beteiligung des IMS möchte das ARTEMIS-Konsortium für dieses Krankheitsbild eine effiziente, digitale Gesundheitsversorgung bereitstellen. Die zentrale Innovation besteht in einer miniaturisierten EKG-Elektronik auf der Grundlage künstlicher Intelligenz, die Vorhofflimmern in Echtzeit direkt am Patienten erkennt.

Belastungsprofile von Astronauten erfassen für sicherere Flüge ins All: Mithilfe des Sensorsystems AI-Suit kann der Blutdruck im Raumanzug gemessen werden

Zukünftig werden mehr Personen ins All fliegen, die nicht dem körperlichen Profil von professionellen Astronautinnen und Astronauten entsprechen. Dafür müssen Raumanzüge noch sicherer werden, um die Belastung der Menschen zu überwachen. Das Fraunhofer IMS hat das Messsystem AI-Suit entwickelt, welches innerhalb des Raumanzuges die Vitalparameter des Tragenden misst, um die Belastung monitoren zu können.

Einfach einzusetzende und effizientere GaN-Leistungsmodule

Im Projekt GaNext (kurz für GaN-Leistungsmodule der nächsten Generation) soll die Einstiegshürde in der Nutzung von Galliumnitrid-Halbleitern (GaN) herabgesetzt und gleichzeitig die Effizienz und Kompaktheit von GaN-basierten Modulen für die Leistungselektronik verbessert werden. Der Schwerpunkt des Projekts liegt in der Entwicklung eines intelligenten Leistungsmoduls (engl. IPM, intelligent power module) genannt, welches auf GaN-Bauteilen basiert. Diese werden mit Gate-Treibern und einer programmierbaren, ausfallsicheren Steuereinheit mit integrierten Schutzschaltungen kombiniert. Die Integration der einzelnen Komponenten in ein kompaktes Gehäuse erhöht die Benutzerfreundlichkeit für den Endanwender.

Kompaktere, effizientere und ausfallsicherere Leistungselektronik für Zukunftstechnologien wie Drohnen, Elektroflugzeuge oder kollaborative medizinische Roboter

PowerCare implementiert ein neues Überwachungskonzept in Form eines miniaturisierten Motorcontrollers mit integrierter Echtzeit-Ausfallvorhersage und legt damit den Grundstein für eine neue Evolutionsstufe intelligenter Leistungsmodule. Zu diesem Zweck werden KI-basierte Vorhersagemodelle auf einem domänenspezifischen RISC-V-Steuerungs-SoC implementiert und mit hocheffizienten GaN-Leistungstransistoren zu einem Leistungsmodul kombiniert.

Gefördert im Rahmen der Internen Programme der Fraunhofer-Gesellschaft, Fördernummer PREPARE 40-06175.

KI-Algorithmen direkt auf dem Chip ausführen: Unser RISC-V-Prozessor, AIRISC-POWER, steigert Energieeffizienz und Zuverlässigkeit von Leistungselektroniksystemen

Das Horizon-KDT-Projekt R-PODID zielt darauf ab, die Energieeffizienz und die Zuverlässigkeit von Leistungselektroniksystemen und -modulen zu erhöhen. Dies soll durch die Integration von künstlicher Intelligenz auf eingebetteten Geräten in das Leistungsmodul ermöglicht werden. Die Projektpartner werden sich dieser Herausforderung aus verschiedenen Blickwinkeln stellen:

- Erforschung spezifischer KI-Algorithmen und deren Einsatz auf ressourcenbeschränkten Geräten

- Entwicklung von Hochleistungs-Halbleiterbauelementen auf der Grundlage von GaN- und SiC-Technologien (Siliziumkarbid), die den Anforderungen der modernen Industrie und der E-Mobilität entsprechen

- Einsatz innovativer Sensoren und Gehäuselösungen zur Erfassung von Echtzeitdaten, die als Input für KI-Modelle verwendet werden, um die Robustheit der Energiesysteme zu verbessern

Das Fraunhofer IMS passt sein AIRISC-POWER-Design im Rahmen des Projekts an, um die KI-Algorithmen direkt auf dem Chip ausführen zu können.

R-PODID ist ein EU-Projekt und wird gefördert unter folgender Nummer: 101112338 — R-PODID — HORIZON-KDT-JU-2022-2-RIA.

»ASIL-D ready« Sicherheitscontroller für eine autonome Drohne

Der Albatros gehört zu den effizientesten Segelflugvögeln. Seine enorme Wendigkeit und sein müheloses Schweben auf Luftströmungen über Tausende von Kilometern sind bewundernswert. Ein Konsortium aus sechs Fraunhofer-Instituten will sich dieses Phänomen aus der Natur abschauen und mit dem ALBACOPTER® ein Fluggerät entwickeln, das nicht nur fantastisch schwebt, sondern auch effizient starten und landen kann.

Das Fraunhofer IMS hat eine Sicherheitssteuerung für unbemannte Flugobjekte (engl. UAVs, Unmanned Aerial Vehicles) entwickelt, den AIRISC-SAFETY, der als »ASIL-D ready« (automotive safety integrity level) zertifiziert ist. Der RISC-V-Prozessor AIRISC des Fraunhofer IMS wurde angepasst, um die Überwachung der Kommunikationsschnittstellen und die Anbindung der autonomen Drohne an das Busnetz sicherzustellen.

Forschungsplattform für das Thema »vertrauenswürdige Elektronik«

Um Elektronik sicher und zuverlässig einzusetzen, muss man nachvollziehen können, woher sie kommt, was sie macht und wie sie aufgebaut ist. Aktuell gibt es zwar einige technische Lösungen im Sinne einer vertrauenswürdigen Elektronik, aber noch keine durchgängige Methodik zur Vertrauenswürdigkeit, die die komplette Wertschöpfungskette ausreichend einbezieht. Dies ist der Ausgangspunkt des im März 2021 gestarteten Forschungsprojekts Velektronik.

Neuartige Designmethoden für vertrauenswürdige Elektronikschaltungen

Im Projekt VE-DIVA-IC arbeiten das Fraunhofer IMS und das Fraunhofer AISEC mit weiteren Partnern daran, den Schutz von Integrität und Identität elektronischer Bauteile in den Bereichen Mobilität und Automatisierungstechnik zu stärken. Durch einen zusätzlichen Schritt beim Entwurf von integrierten Schaltungen können so elektronische Komponenten, etwa in Fahrzeugen, vertrauenswürdig abgesichert werden.

Sensorik für kontaktlose Vitalparametermessung zur Entlastung von Pflegekräften und Linderung des Fachkräftenotstands

Im Projekt CAREFUL EDGE X entwickelt das Fraunhofer IMS zusammen mit weiteren Partnern eine intelligente Lösung für die Pflege, die durch die kontaktlose Erfassung und lokale Verarbeitung von Vitalparametern über Edge-Computing funktioniert. Das Fraunhofer IMS steuert im Projekt das Know-how für die kontaktlose Sensorik zur Erfassung von Vitalparametern in einem intelligenten Pflegezimmer bei. Zusammen mit anderen Geräten wie einem Pflegebett, einem Sitzkissen und einem Pflegeroboter werden die Daten validiert und genutzt, um die Pflege zu optimieren. Die Kommunikation zwischen den Geräten wird über eine digitale Pflegeplattform und -software abgewickelt. Das Projekt CAREFUL EDGE-X verbindet so die Bereiche Pflege, Robotik und Smart Living und ermöglicht eine sektorübergreifende Nutzung. Durch die lokale Datenverarbeitung am Edge wird der Energieverbrauch in Cloud-Rechenzentren reduziert, was dem Klima- und Umweltschutz zugutekommt.

Im Video erfahren Sie, wie unsere KI-basierte, kontaktlose Vitalparametermessung die Pflege revolutionieren kann

Höhere Energieeffizienzen und Prozessoptimierungen für eine Industrie im Wandel

Edge AIoT (engl. AI integrated in the Internet of Things) ist nicht nur ein Trend, sondern für die Industrie auch immer häufiger notwendig. Vermehrt müssen kleine Geräte mit einer geringen Latenz riesige Datenmengen nahe am Ort der Entstehung verarbeiten und gleichzeitig effizient KI-Algorithmen ausführen. Daher ist im Rahmen von industriellen Anwendungen eine kontinuierliche Verbesserung von Hardware zur Berechnung von KI-Algorithmen vonnöten. Dieser Herausforderung widmen sich 19 Unternehmen und Universitäten im Forschungsprojekt CLEVER.

Mit AIfES® KI auf jeder Hardware implementieren

Mit dem Open Source KI-Software Framework AIfES® (Artifical Intelligence for Embedded Systems) kann man künstliche neuronale Netze (KNN) praktisch auf jeder Hardware ausführen und sogar trainieren. Kleine Embedded Systeme plus künstliche Intelligenz – das Thema unserer Zeit.

Erfahren Sie mehr über AIRISC auf Google Scholar.

/github-mark.png)