Neue KI-Hardwarebeschleunigung für smarte Sensorik am Fraunhofer IMS

RISC-V Prozessor AIRISC beschleunigt die Auswertung von Sensordaten um 80 %

Der RISC-V Prozessor, eine 32-Bit RISC (Reduced Instruction Set Computer) Architektur, AIRISC verfügt ab sofort über Befehlssatzerweiterungen und Coprozessoren zur effizienten Berechnung von neuronalen Netzen. Für eine medizinische Anwendung zur Erkennung von Vorhofflimmern in EKG-Daten haben wir in der Auswertung einen Geschwindigkeitsvorteil von über 80 % bei nur 10 % höherem Flächen- und Energiebedarf erreicht.

AIRISC und die aktuelle Forschung an anwendungsspezifischen Erweiterungen

Seit Anfang 2022 ist der RISC-V Prozessor AIRISC für Embedded- und Sensorikanwendungen in der Basis-Variante als freier Download auf GitHub verfügbar. Diese Version steht unter der permissiven Solderpad-Lizenz und ist mit Beispiel-Projekten für verschieden FPGA-Entwicklungsboards ausgestattet. Die Lizenz erlaubt nicht nur das Testen des Cores, sondern auch den Einsatz in kundenspezifischen und kommerziellen Anwendungen. Zur Unterstützung forscht das Fraunhofer Institut für Mikroelektronische Schaltungen und Systeme an modularen, anwendungsspezifischen Erweiterungen, beispielsweise für Echtzeit-Regelungen in der Leistungselektronik, für die Signalanalyse in medizinischen Anwendungen und für 3D-Bildverarbeitung mittels LIDAR.

Das neue Beschleuniger-Paket

Das neueste Ergebnis dieser Entwicklungen ist ein Paket von Beschleunigern für die effiziente Ausführung von neuronalen Netzen. Mit den Beschleunigern funktionieren moderne KI-Algorithmen auch auf energiekritischer Hardware, wie z. B. energieautarken Sensorsystemen. Zur Erstellung von Benchmarks haben wir neben Tensor Flow Lite auch unser optimiertes Software-Framework »AI for Embedded Systems – AIfES« auf den AIRISC-Core portiert.

Das aktuelle Erweiterungspaket von AIRISC besteht aus zwei Komponenten:

1. Eine Sammlung von Hardware-Beschleunigern für gängige Aktivierungsfunktionen (AF). Hierzu zählen mit Stand März 2022 tanh, sigmoid, softsign sowie softmax auf Basis der e-Funktion.

2. Die parallele Ausführung mehrerer Multiplikations- und Addier-Operationen (Multiply-Accumulate) zur Beschleunigung von Matrix-Multiplikationen. Aktuell werden die Datentypen 16-Bit Integer (2-fach parallel) und 8-Bit Integer (4-fach parallel) unterstützt. Die Erweiterung ersetzt die Standard-ALU (Arithmetical Logical Unit) und benutzt den minimal möglichen Overhead an Hardware bei maximaler Geschwindigkeit durch direkte Integration in die Pipeline des Prozessors. Diese zusätzlich eingeführten SIMD-Instruktionen (Single Instruction Multiple Data) sind kompatibel zu der P-Extension der RISC-V Spezifikation für DSP-Anwendungen, die sich aktuell in der Ratifizierungsphase befindet.

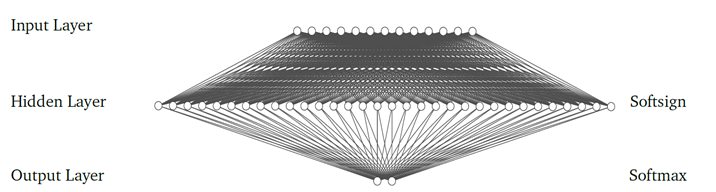

Als Benchmark für die beschriebenen Beschleuniger dient ein Feed-Forward Neuronales-Netz mit 13 Neuronen im Input-Layer, einem Hidden-Layer mit 17 Neuronen sowie zwei Neuronen im Output-Layer. Dieses Netz stammt aus einer Anwendung zur Untersuchung von EKG-Daten auf Anzeichen für Vorhofflimmern.

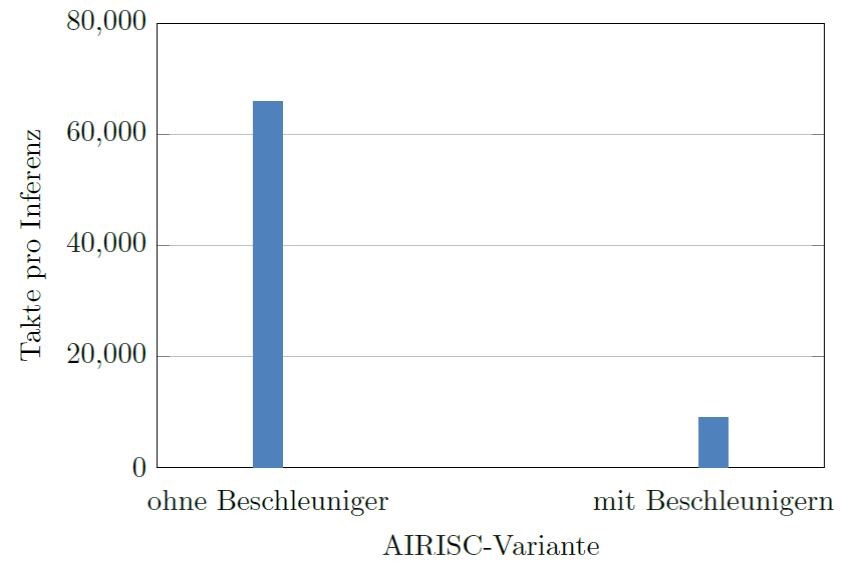

Durch die Verwendung der Hardware-Beschleuniger lässt sich ein Geschwindigkeitsvorteil von mehr als 80 % bei der Ausführung des neuronalen Netzes erzielen (Abb. 1). Neben der parallelen Ausführung der Matrix-Multiplikationen wird hier ebenfalls ein großer Anteil an Speicherzugriffen eingespart, weshalb die Verbesserung deutlich über dem zu erwartenden Faktor vier liegt.

Der verwendete Datentyp ist 8-Bit Integer. Als Aktivierungsfunktionen kommen softsign für den Hidden-Layer und softmax für den Output-Layer zum Einsatz (Abb. 2).

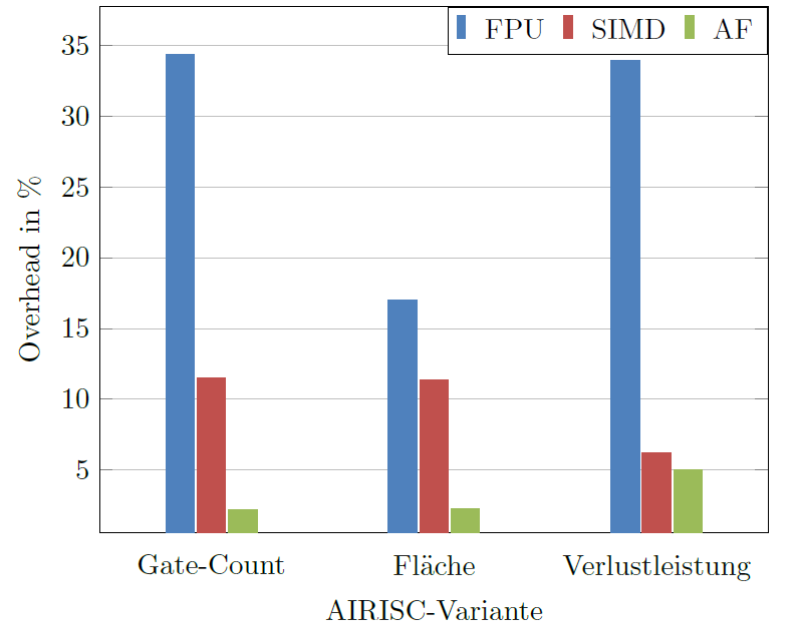

Abbildung 3 zeigt den Overhead an Hardware-Gattern (Gate-Count), Fläche und Verlustleistung, den die beschriebenen Beschleuniger mit sich bringen. Die Werte beziehen sich beispielhaft auf die Synthese des Prozessors für eine 0,18 µm CMOS-Technologie. Zusätzlich ist der Platzbedarf dargestellt, welchen die ebenfalls für den AIRISC verfügbare Hardware-Fließkommaeinheit (Floating Point Unit: FPU) mit sich bringt.

Die nächsten Schritte mit AIRISC am Fraunhofer IMS

Dem enorm hohen Geschwindigkeitsvorteil steht ein sehr moderater Overhead an Hardwareaufwand gegenüber. Durch die signifikante Reduktion der Betriebsfrequenz kann so ein erheblicher Anteil der benötigten Leistungsaufnahme des Systems eingespart werden. Details wurden beim fünften Treffen der Duisburger RISC-V Gruppe präsentiert. Der Vortrag ist über den Youtube-Kanal von RISC-V International abrufbar.

Mit dem »AIRISC-PWR« bietet das Fraunhofer IMS bereits eine integrierte RISC-V PWM- und Regler-Lösung für den Einsatz in der Leistungselektronik an. Eine strahlungsresistente Variante des AIRISC für den Einsatz in physikalischen Großexperimenten ist ebenfalls verfügbar. Daneben entwickeln wir bereits das nächste Mitglied der AIRISC-Familie: »AIRISC-LIDAR« ist ein auf die Verarbeitung von LIDAR-Rohdaten spezialisierter Satz von Erweiterungen für die Verwendung in FPGA und ASIC.

Das Fraunhofer IMS erweitert zudem schrittweise die Safety Variante des AIRISC »AIRISC-SFTY« für Anwendungen mit Anforderungen an die funktionale Sicherheit. Dieser Safety-AIRISC verfügt über Mechanismen wie Dual-Core Lockstep, ECC Speicherabsicherungen (Error Correcting Code) und Hardware-Watchdog und ist gemäß ISO 26262 ASIL-D Ready zertifiziert. Er wird Mitte 2022 verfügbar sein.

Weitere Informationen und Datenblätter finden Sie unter www.airisc.de

Anfragen richten Sie bitte an Herrn Carsten Rolfes, Programmleiter Vertrauenswürdige Elektronik sowie Herrn Alexander Stanitzki, Geschäftsfeldleiter Industry.