Fraunhofer IMS has more than 30 years of experience in CMOS technology development and operated as development and production basis a complete 200 mm CMOS line with different robust CMOS processes up to a minimal structure of 0.35 µm.

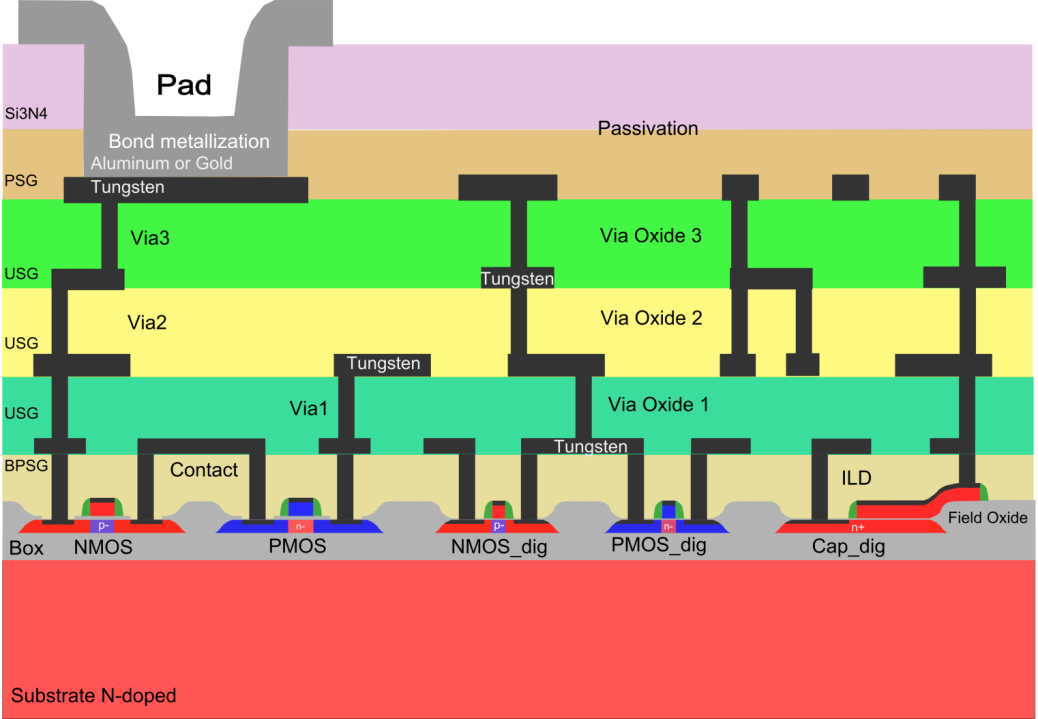

In this line there is a specific high temperature resistant Silicon-On-Insulator (SOI) CMOS technology available. Individual transistors are not isolated via diodes (pn junctions), but dielectrically by a buried oxide, reducing leakage currents by up to three magnitudes. An additional optimization of the devices enables a performant operation of integrated circuits in up to 300 °C. To increase the reliability even further and to reduce the degradation of electromigration the technology is also equipped with tungsten instead of the commonly used aluminum metallization. The minimal structure size of 0.35 µm and up to four metal layers allow for the realization of compact integrated systems including small embedded microcontrollers.