Neuigkeiten rund um den RISC-V Prozessor AIRISC

AIRISC – der RISC-V Prozessor für Smarten Sensoren und Embedded KI Anwendungen des Fraunhofer IMS

Neuigkeiten rund um die AIRISC-Familie von RISC-V-Cores des Fraunhofer IMS.

Der AIRISC ermöglicht effizientes maschinelles Lernen und KI in Sensoren, IoT-Geräten und anderen eingebetteten Anwendungen. Das freie RISC-V Prozessor Instruction Set ist ideal geeignet, um kundenspezifische Erweiterungen in kurzer Zeit zu implementieren und so eine optimale Performance für spezielle Anwendungen bereitzustellen. Im Zusammenspiel mit der vom Fraunhofer IMS entwickelten AIfES-Softwarebibliothek, unterstützt die AIRISC-Prozessorfamilie die Inferenz und das Training von neuronalen Netzen direkt auf dem eingebetteten Gerät.

Hierzu haben wir Ihnen aktuelle Ergebnisse und Entwicklungen zusammengestellt. Mehr technische Details zum AIRISC finden Sie im Produktinfoblatt, dass unter www.airisc.de zum Download zur Verfügung steht.

Erfolgreicher AIRISC Tapeout

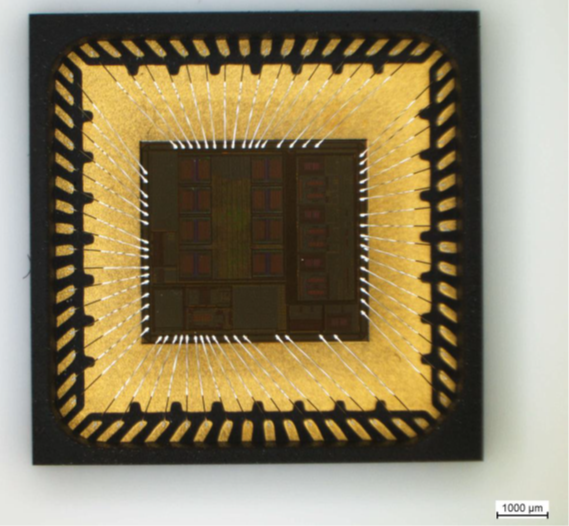

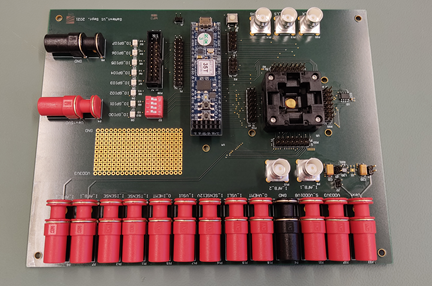

In zwei Projekten sind mittlerweile lauffähige Chips mit dem AIRISC als zentralem Prozessor zur Steuerung und Datenverarbeitung entstanden. Dabei wurde die 180 nm Technologie von XFAB verwendet und die Chips von den Kollegen vom Fraunhofer ENAS mit einem Gehäuse versehen, so dass sie aktuell ausgiebig am IMS getestet werden.

Im DFAM Projekt SichEL wurde der AIRISC mit einer kapazitiven Physical Unclonable Function gekoppelt, um so eine eindeutige Identifikationsnummer zur Nachverfolgbarkeit des Chips innerhalb der Lieferkette zu generieren. Außerdem ermöglicht die PUF die Ableitung von kryptografischen Schlüsseln.

Im Projekt GaNext wurde der AIRISC um Safety Mechanismen, Beschleunigung für KI Algorithmen, Mehrkanal ADC und eine hochpräzise PWM Generierung zur Steuerung von GaN Power Modulen erweitert.

Kommende Updates in 2022

Veröffentlichung einer Open Source Version

Um Interessenten den Einstieg mit dem AIRISC zu erleichtern und auch die Möglichkeit zu geben selbst Anpassungen vorzunehmen, bereiten wir gerade die Veröffentlichung einer Basis Version unter Open Source Lizenz vor.

Zu der frei verfügbaren Version werden, neben dem eigentlichen Prozessor-Core und den Erweiterungen M, C und F, auch gängige Peripherals wie ein MTIME kompatibler Timer oder Schnittstellen wir GPIO, UART und SPI gehören. Der frei verfügbare AIRISC ermöglicht so bereits den Einsatz unter realen Bedingungen.

Produkt AIRISC wird ASIL-D ready zertifiziert

Außerdem arbeitet das Fraunhofer IMS an einer ASIL-D ready zertifizierten Dual-Core Lockstep Variante des AIRISC für sicherheitskritische Anwendungen, z.B. im Automotive Sektor.

Beide Varianten werden im Laufe des Jahres 2022 zur Verfügung stehen.

KI Erweiterungen

Ebenfalls im ersten Halbjahr 2022 wird es eine spezielle Version des AIRSC für Tiny-ML Anwendungen geben. Durch die hardwareseitige Unterstützung der RISC-V ISA P-Extension und die Integration verschiedener HW-Aktivierungsfunktionen ermöglicht der AIRISC zusammen mit dem KI Framework AIfES neue Anwendungsmöglichkeiten. Neben der Ausführung von KI Modellen wird so auch das Training direkt in Mikrokontrollern ermöglicht.

RISC-V Duisburg Meetup

Unser Mitarbeiter Alexander Stanitzki ist zusätzlich als RISC-V Ambassador unterwegs und richtet die, leider aktuell nur digitalen, Meetups der RISC-V Gruppe Duisburg aus.

In 2021 gab es bereits 3 Veranstaltungen in denen aktuelle Entwicklungen rund um den AIRISC und durch Gastredner aus dem RISC-V Ökosystem vorgestellt wurden. Die Videos der vergangenen Veranstaltungen sind online abrufbar und das nächste Treffen ist am 16.Februar 2022 geplant.

AIRISC im strahlungsharten Chip - Tapeout der FH Dortmund

Neben eigenen Chips wird der AIRISC auch erfolgreich durch Partner verwendet. Das Team des Labor für "Integrierten Schaltungsentwurf" an der FH Dortmund, um Prof. Michael Karagounis und dem Doktoranden Alexander Walsemann hat mit dem AIRISC einen strahlungsharten, dreifach-redundanten Chip in einer 65 nm Technologie von TSMC gebaut.

LinkedIn Produktseiten AIRISC und AIfES

Wir sind jetzt auch auf Linkedin unterwegs. Wenn Sie Sich für aktuelle Information zu den Produkten AIRISC, dem RISC-V Prozessor des Fraunhofer IMS oder dem Embedded KI Framework AIfES interessieren schauen Sie vorbei.

AIfES – KI Framework

AIRISC –RISC-V Prozessor für Safety, Security und KI