Das Fraunhofer IMS besitzt mehr als 30 Jahre Erfahrung in CMOS Technologieentwicklung und betreibt als Entwicklungs- und Fertigungsbasis eine vollständige, 200 mm CMOS-Linie mit verschiedenen robusten CMOS-Prozessen bis zu einer minimalen Strukturgröße von 0,35 µm.

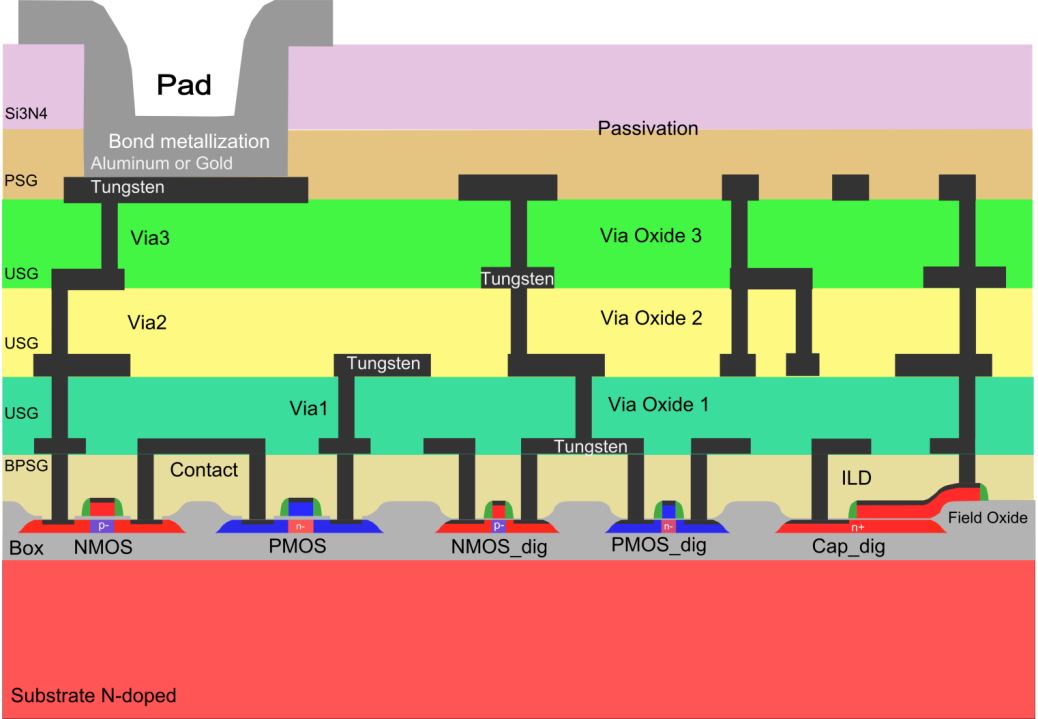

Unter anderem steht in dieser Linie eine spezifische hochtemperaturfähige Silicon-On-Insulator (SOI) CMOS Technologie zur Verfügung. Einzelne Transistoren werden dabei nicht mehr über Dioden (pn-Übergänge), sondern dielektrisch durch ein vergrabenes Oxid voneinander isoliert was die Leckströme um bis zu drei Größenordnungen reduziert. Eine zusätzliche Optimierung der Bauelemente ermöglicht einen performanten Betrieb von integrierten Schaltungen bis 300 °C. Um die Zuverlässigkeit weiter zu erhöhen und Degradation durch Elektromigration zu reduzieren, ist die Technologie außerdem mit einer Wolfram- anstelle der sonst üblichen Aluminiummetallisierung ausgestattet. Die minimale Strukturgröße von 0,35 µm und bis zu vier Metalllagen erlauben die Realisierung von kompakten integrierten Systemen einschließlich kleiner eingebetteter Mikrocontroller.