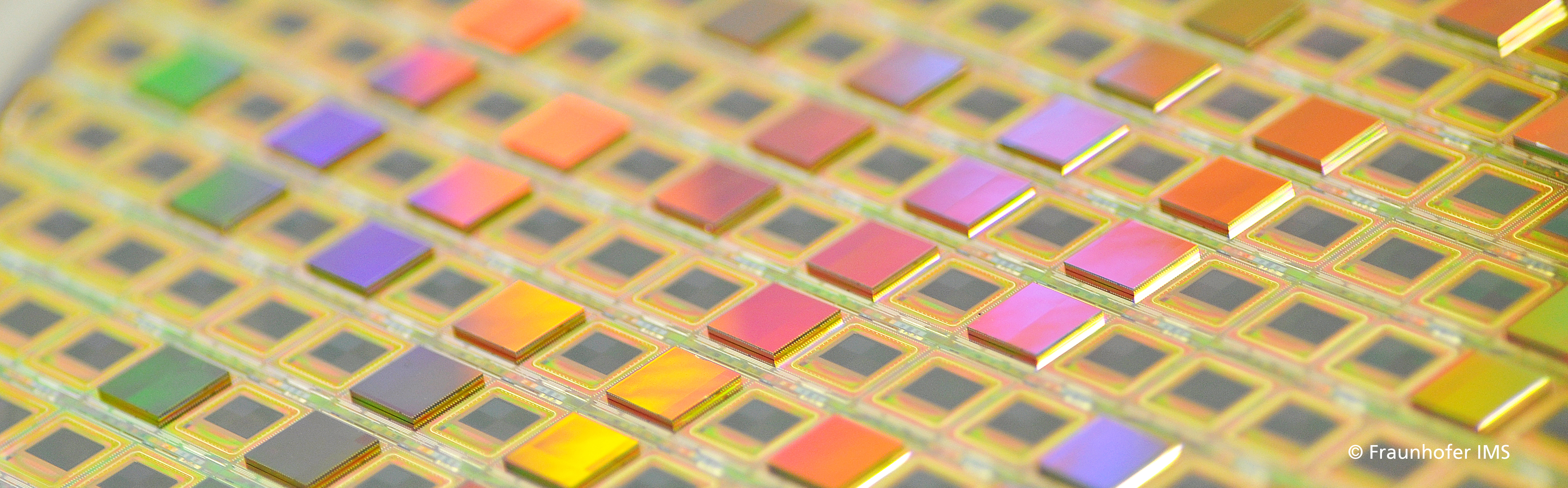

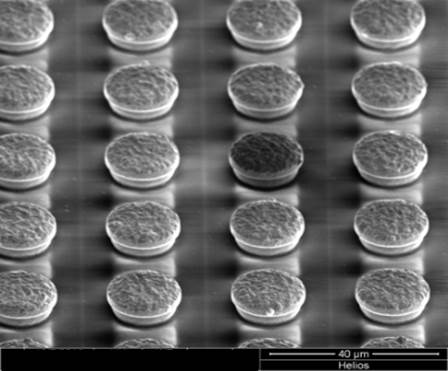

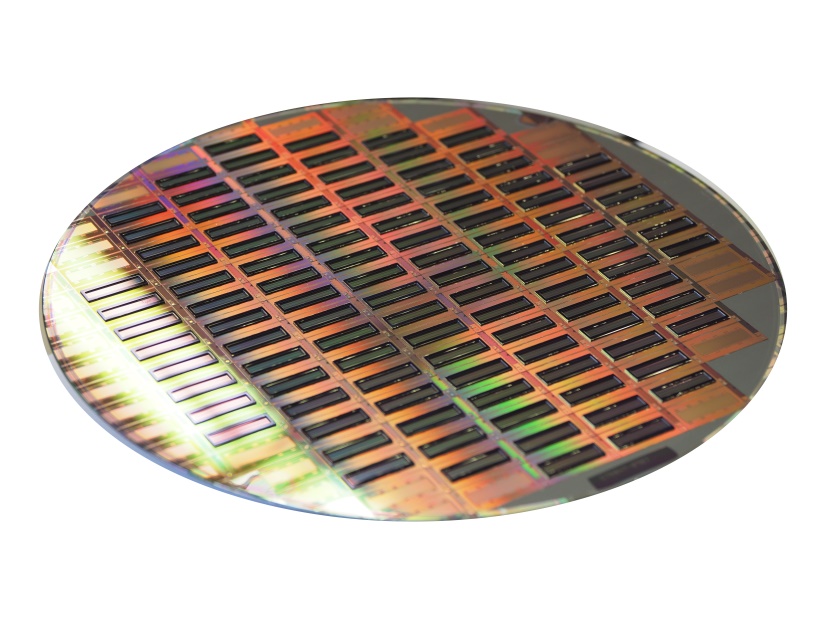

Nutzen Sie den Service und das Know-How des Fraunhofer IMS im Bereich CMOS und Mikrosystemtechnik zur Entwicklung innovativer und kompakter Mikrosysteme.

Das Fraunhofer IMS verfügt über eine 30-jährige Erfahrung im Bereich der CMOS Technologieentwicklung und hat sich im Bereich Devices and Technologies vor allem auf folgende Themengebiete fokussiert: