Das technologische Spektrum für leistungsfähige CMOS Bildsensoren

Die technologische Basis für die umfangreiche Palette optischer Sensoren ist die CMOS Technologie. Seit mehr als 30 Jahren entwickelt und fertigt das IMS CMOS Bildsensoren. War es zunächst der Standard CMOS Prozess, der bereits verschiedene Fotodioden bereitstellt und erste Produktentwicklungen ermöglichte, so wurden später spezielle optoelektronische Bauelemente und Prozessschritte entwickelt, die die Eigenschaften und Vielseitigkeit der Sensorlösungen stets verbesserte. Spezielle Dioden und Detektorelemente wie

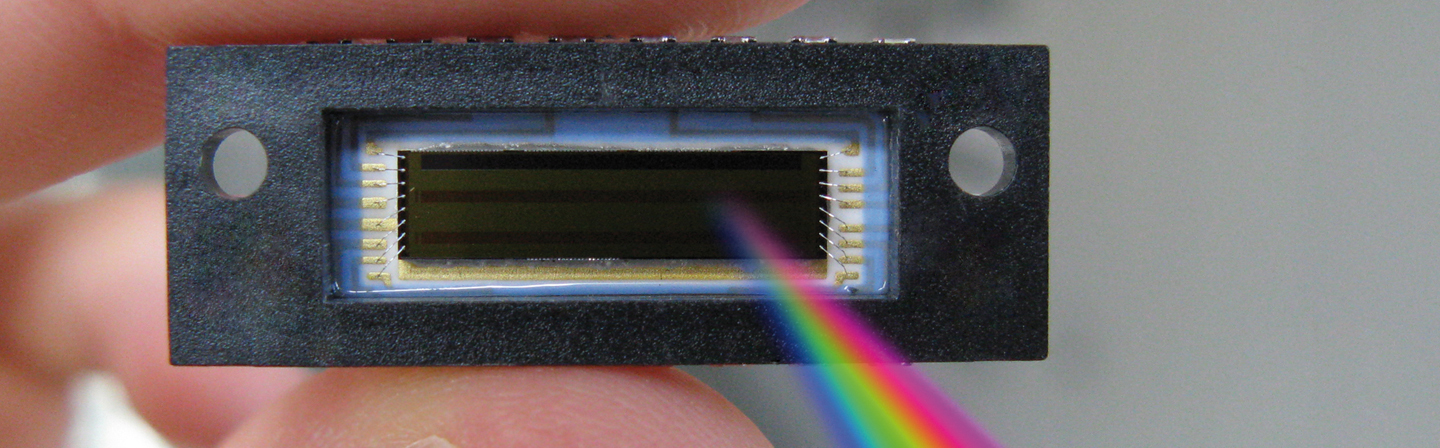

für verschiedene Anwendungen wie Röntgen, Spektroskopie, Time-of-Flight, LiDAR oder Time-Delay-Integration wurden in dem Standard CMOS Prozess entwickelt und integriert. Ferner stehen spezielle Prozessoptionen wie

- Stitching

- UV-transparente Passivierung

- Planarisierung

- Farbfilter

- Mikrolinsen

für Produktentwicklungen zur Verfügung.

Die im IMS installierte 0,35 µm CMOS-Technologie ist nach dem Automobil Standard ISO TS16949 qualifiziert und damit äußerst stabil und zuverlässig. Die Integration eines neuen Bauelementes in diesen Prozess bedeutet extremen Aufwand, Entwicklung und Qualifizierung, bevor eine Produktentwicklung starten kann.

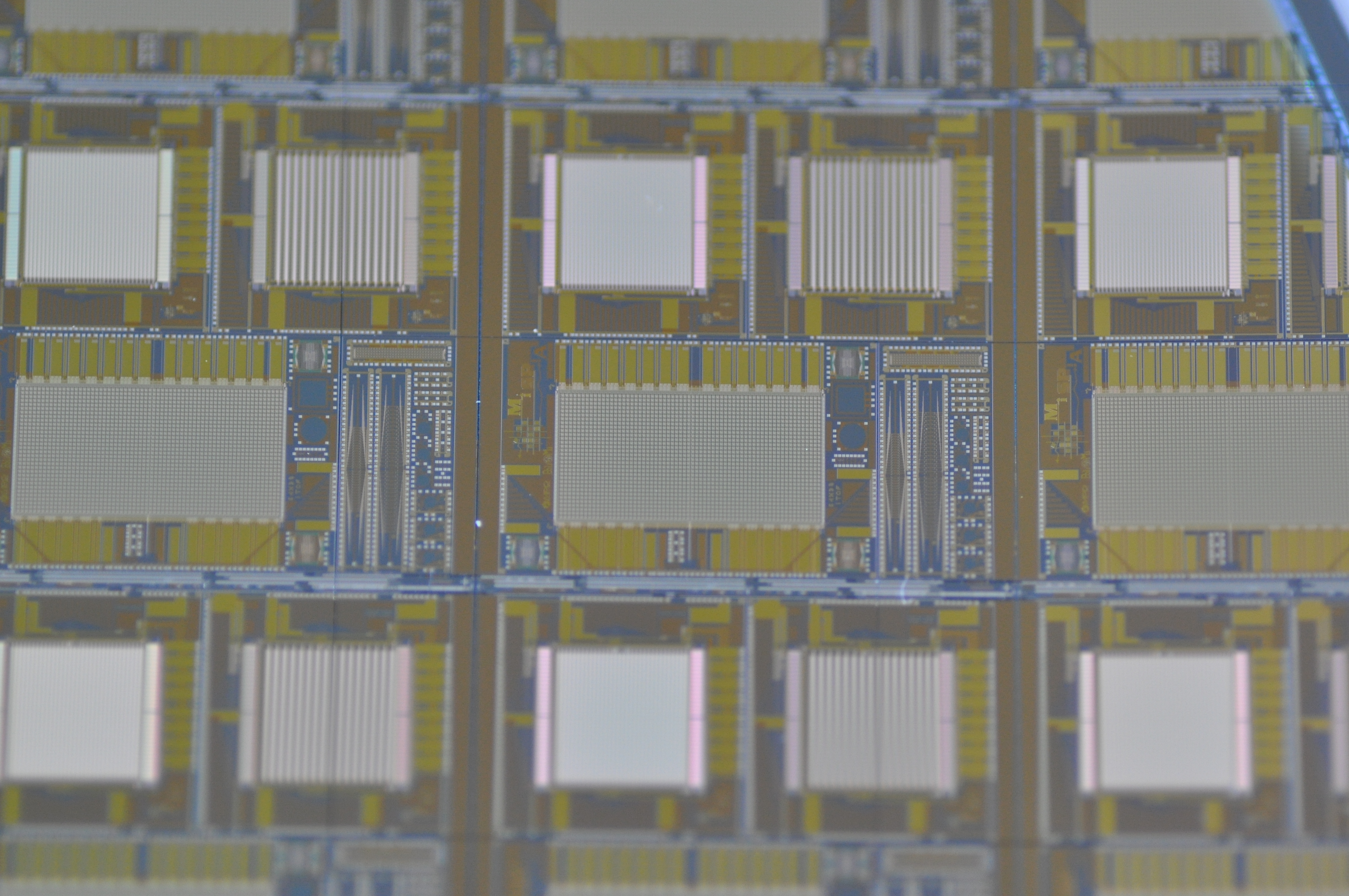

Eine neuerdings verfügbare Technologiebasis für die optischen Sensoren bildet die 3D-Integration im MST Lab&Fab des Fraunhofer IMS. So ist es möglich, sehr kompakte und smarte BackSide Illuminated optische Sensoren zu erzeugen.Hierbei befinden sich die Detektorelemente und die Ausleseschaltung auf zwei unabhängigen Chips, die durch einen Löt- oder Bond-Prozess miteinander verbunden werden. Diese hybride Integration von »Chiplets« erfolgt entweder als Chip-to-Wafer oder für größere Stückzahlen als »Wafer-to-Wafer« Prozess. Die Vorteile liegen auf der Hand: die beiden Wafer oder Chips können unabhängig voneinander gewählt und optimiert werden. Für die SPAD Arrays zum Beispiel bedeutet das, dass ein Kompromiss »gute SPAD-Eigenschaften« vs. »kompakte Elektronik« nicht länger erforderlich ist. Die SPADs können für die richtige Wellenlänge optimiert werden und die Elektronik kann in kleineren Strukturgrößen auf kleinster Fläche untergebracht werden. Die Technologie der 3D-Integration befindet sich mittlerweile in der Qualifizierungsphase.