## The technology

### Precise surface coating at atomic level

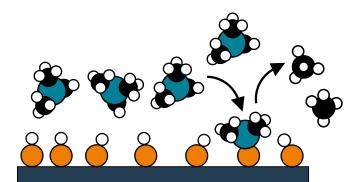

Atomic Layer Deposition (ALD) technology is the preferred method for creating ultra-thin layers. It allows precise control of layer thickness, ranging from 1 nm to 100 nm, thanks to its low deposition rate. Additionally, ALD processes can be conducted at temperatures between 200 °C and 400 °C, making them compatible with CMOS technology.

### Key benefits of ALD

- Perfect conformity for depositions with a high aspect ratio and excellent side wall coverage

- High precision of the layer thickness

- High quality of the deposited layer

- Low deposition temperature compared to CVD techniques

### Contact

Business Unit Industry sales@ims.fraunhofer.de

Fraunhofer Institute for Microelectronic Circuits and Systems IMS Finkenstraße 61 47057 Duisburg www.ims.fraunhofer.de/en.html

**Copyright** Fraunhofer IMS, Duisburg 2023 electronic Circuits and Systems IMS

Fraunhofer Institute for Micro-

**Fraunhofer**

Tools, materials and applications

# Atomic Layer Deposition

## Our expert team

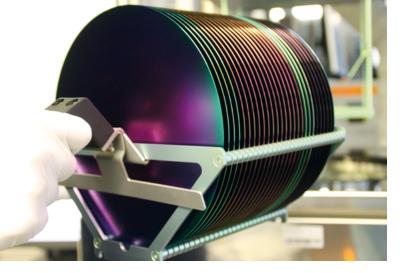

At Fraunhofer IMS, the ALD tool ensemble can process various types of 200 mm wafers. These can be silicon or glass wafers, including those with CMOS circuits.

Our ALD technology has already enabled numerous scientific publications and multiple patents. Because of our extensive know-how, we act as the ALD competence center within Research Fab Microelectronics Germany (FMD), which is Europe's biggest research group for applications and systems in micro- and nanoelectronics.

## Fraunhofer IMS

## Smart Sensor Systems for a safe, secure, and sustainable future

As a trusted research and development partner for industry, our goal is to develop customized sensor systems for your specific needs in the areas of biomedical sensors, optical systems, open source semiconductors, embedded AI, technology services, and even quantum technology.

The teams in the four business units – **Health, Industry, Mobility, and Space and Security** – are committed to implementing outstanding and versatile microelectronics that can be utilized across all your projects. For example, these solutions feature high integration capability, enormous energy efficiency, and reliable functionality even under harsh conditions.

# Materials and their properties

| Material                       | Properties                                                    |

|--------------------------------|---------------------------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | Protective layer, medium-k dielectric,<br>biocompatible       |

| Ta <sub>2</sub> O <sub>5</sub> | Protective layer, high-k dielectric,<br>biocompatible         |

| ZnO                            | Transparent conductive layer                                  |

| AZO                            | Transparent conductive layer                                  |

| TIAICN                         | Conductive layer, barrier                                     |

| TiN                            | Conductive layer, barrier                                     |

| Ru                             | Conductive layer, electrical or optical shield, biocompatible |

| MoS <sub>2</sub>               | Semiconducting 2D material                                    |

| WS <sub>2</sub>                | Semiconducting 2D material                                    |

| SiO <sub>2</sub> (from 2024)   | Protective layer                                              |

| <b>Cu</b> (from 2024)          | Conductive layer                                              |

With our outstanding knowledge in **precursor chemistry**, we offer **process benchmarking** with new and established precursors in our R&D tool and process development of new materials like LiPON, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, and more. Even **special substrates** like polymers can be coated with ALD materials in our **low-temperature** processes.

## Our tools

We can carry out ALD processes on wafer, batch and chip level with four different ALD tools.

### ALD mini (PICOSUN® R-200 std.)

- R&D of new materials

- Can be loaded manually with 200 mm wafers as well as any wafer and chip size below Ø 200 mm

#### ALD cluster (PICOSUN® R-200 adv.)

- Allows automatic handling and successive processing of 25 wafers of 200 mm

- Two chambers are designed for thermal ALD and plasmaenhanced ALD, respectively

### ALD batch (PICOSUN® P-300B)

25 wafers of 200 mm can be processed simultaneously with homogeneous quality, aiming for a high throughput

### F.A.S.T.-ALD (Plasma-Therm F.A.S.T.®)

- Four-chamber system specialized for TSV and μVia production necessary for wafer stacking

- The automatic handling of 200 mm wafers is configured to process a whole 25 wafer batch successively

ALD involves a multi-stage deposition process. A typical sub-step is shown below.

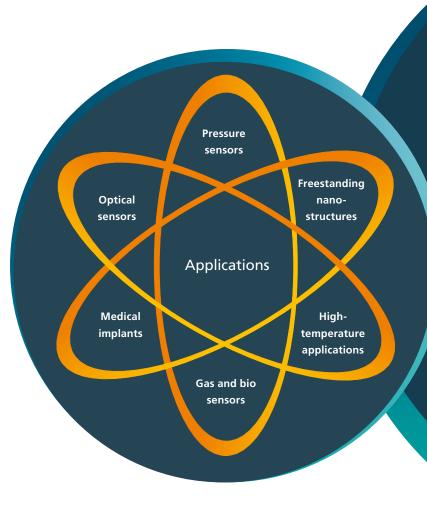

# Applications

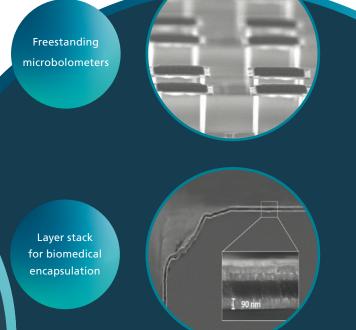

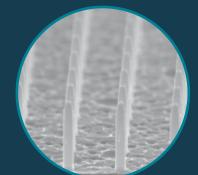

ALD technology can be utilized in a **broad spectrum of applications, from post-CMOS to MEMS and NEMS**. The implementation of freestanding nanostructures on top of integrated circuits increases the density of sensors. In particular, ALD allows the formation of high-aspect-ratio 3D structures consisting of ultra-thin layers while being extensive in other dimensions. These structures can be **nanowires, ultra-thin membranes, or cantilevers**.

## Work samples

Find a few examples of our work from the scanning electron microscop below.