## FRAUNHOFER INSTITUTE FOR MICROELECTRONIC CIRCUITS AND SYSTEMS IMS

2 ALD-Passivation layers on CMOS-Passivation

## Fraunhofer Institute for Microelectronic Circuits and Systems IMS

Finkenstraße 61 D - 47057 Duisburg phone +49 203 37 83-0 fax +49 203 37 83-266 www.ims.fraunhofer.de

contact Michael Bollerott phone +49 203 3783-227 vertrieb@ims.fraunhofer.de

## ALD – CATALYST FOR NEW MEMS/NEMS DEVICES

Atomic layer deposition (ALD): an advanced process technology as a catalyst for new MEMS and NEMS devices

Protective media resistent layers for sensors, optical coatings, high C trench capacitors, new NEMS devices for gassensors, biosensors with nanowires, ultrathin freestanding membranes: all this is possible with the ALDtechnique (Atomic Layer Deposition)

ALD is a thin layer deposition process that relies on chemical surface reactions of at least two chemical precursors that enable layer-by-layer growth of high quality films with thicknesses in the range of typical 1-50 nm. Due to the fact that an increasing range of precursors is available a wide range of materials for different application purposes can be addressed. The key advantages of this process can be summarized as follows:

Very high conformity of the deposited films (see figure 1). A very good side wall coverage of high aspect ratio trenches and holes with ALD-films enables applications for 3D-technologies.

- The deposited films are of high quality and nearly pin hole free

- A growing material diversity is available covering metals, insulators, high-k dielectrics, sensor and optical materials and transparent conductive oxides.

Since the deposition temperatures are comparatively low, ALD-layers can be deposited on CMOS-wafers without any harm to the circuitry. FhG IMS can offer you both from one source.

Thus the atomic layer deposition technique can be utilized for various MEMS- or NEMS (MEMS/NEMS: Micro/Nano Electro Mechanical Systems) and CMOS related applications such as:

Protective media-resistant layers for sensor devices such as pressure sensors or for encapsulations of medical implants. In figure 2 an additional ALD layer stack on a non planarized CMOSpassivation is depicted as an example.

- Aluminium oxide and tantalum pentoxide are available. Further ALDmaterials can be implemented at IMS.

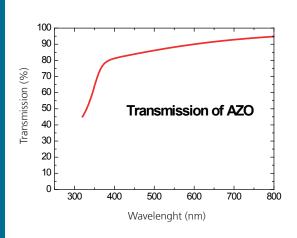

- Electrical or optical shielding can be achieved by metallic layers as ruthenium. Furthermore ALD-layers can be utilized as transparent conductive electrode layers e.g. for optical sensors or solar cell applications (see figure 3).

- Due to its high conformity ALD can be used as an insulating material in trench capacitors. Advantageously high- and medium-k dielectrics are available for trench capacitors. IMS currently develops trench capacitors for high temperature (more than 250°C) applications on basis of ALD layers.

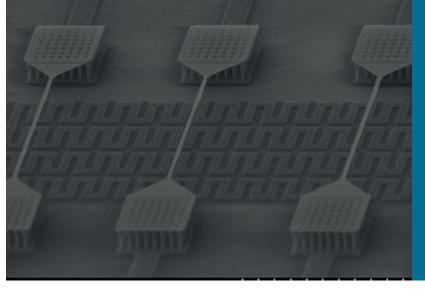

- A very cost effective 3D-NEMS-technology has recently been developed at IMS that enables the creation of free standing Nanostructures on CMOS-

surfaces with only few additional lithographic masks (patent pending). This technology is based also on ALDdeposition.

This novel technology offers the possibility to create freestanding 3D-MEMS or NEMSstructures with wall thicknesses in the nmrange on top of CMOS-surfaces. Due to the availability of a multitude of ALD-materials with different physical and chemical properties and due to the properties related to the free standing structures e.g. nanoscale wall thickness, the low mechanical and thermal mass etc., such structures are ideally suited for advanced sensor applications such as gas- or biosensing e.g. by nanowires or mechanical sensing ultra-thin membranes or cantilevers. In figure 4 free standing Ruthenium-Nanowires generated on a CMOSpassivation are depicted as an example. A special advantage of this novel technique

is connected to the possibility of post-CMOS integration, that enables the development of novel intelligent CMOS integrated sensors or actuators.

At IMS the ALD-technique is available for 200 mm-wafers which is compatible to the IMS 200 mm CMOS wafers. Special solutions for arbitrarily shaped devices as packaged sensors or special materials can be implemented upon request.

- 3 Transmission of ALD-deposited aluminum doped zinc oxide (AZO) serving as a transparent conductive oxide

- 4 free standing 3-D nanostructure based on ALD

| Available ALD-Materials |                                   |                     |                              |                      |                                                    |

|-------------------------|-----------------------------------|---------------------|------------------------------|----------------------|----------------------------------------------------|

| Material                | Typical deposition<br>temperature | Film<br>Homogeneity | Film resistance<br>(typical) | maximum<br>thickness | Typical Application                                |

| Al2O3                   | 200 °C<br>300 °C                  | 98 %                | -                            | 50 nm<br>75 nm       | Protection layer, medium-k dielectric              |

| Ta2O5                   | 275 °C                            | 90 %                | -                            | 15 nm                | Protection layer, high-k dielectric                |

| ZnO                     | 200 °C                            | 96 %                | 5240 μΩcm                    | 75 nm                | Transparent, conductive layer                      |

| AZO                     | 200 °C                            | 96 %                | 2075 μΩcm                    | 75 nm                | Transparent conductive layer                       |

| TiAlCN                  | 400 °C                            | 80 %                | 560 μΩcm                     | 100 nm               | Conductive layer, barrier function                 |

| 1210                    | 400 °C                            | 75 %                | 140 μΩcm                     | 10 nm                | Conductive layer, barrier function                 |

|                         | 350 °C                            | 85 %                | 20 μΩcm                      | 75 nm                | Conductive layer, electrical and optical shielding |